摘 要: 用硬件描述语言verilog HDL 设计实现了一种嵌入式USB2. 0 主机控制器IP 核, 简要介绍了嵌入式USB主机设计背景, 重点描述了USB 主机控制器IP 核的结构划分和各模块的设计分析, 最后给出了nc2verilog 功能仿真方案以及FPGA 验证方案。 通过nc2verilog 功能仿真及FPGA 验证表明, 此IP 核可以作为一个独立模块应用到嵌入式系统中。

1 引言

从通用串行总线(USB) 问世, 到协议规范2. 0版本, USB 在不断自我完善, 并走向成熟。 USB 的拓扑结构中居于核心地位的是主机(Host), 任何一次USB 的数据传输都必须由主机来发起和控制, 而目前, 大量扮演主机角色的是个人电脑( PC)。所有USB 设备都只能在PC 上使用, 只能通过PC 来进行相互的文件和数据交换。 没有了PC, 这些设备就失灵了( 指数据交换的功能)。

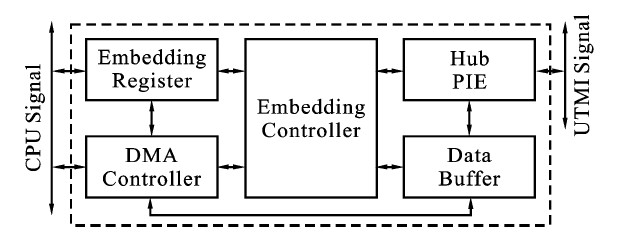

因此, 如何将USB 应用到嵌入式领域? 如何实现USB 点对点的通信?0等问题, 开始进入了USB开发者的讨论议程。 嵌入式USB 主机的设计在国内处于刚刚起步的阶段, 仅有不多的半导体公司提供接口芯片, 还很少有完整的嵌入式USB 主机产品上市。 厂家和USB 论坛所能提供的Demo也限于依靠嵌入式操作系统WinCE 和Linux 等。因此, 项目研究具有一定的领先性。 正是在这种背景下, 业界和用户的需求呼唤USB 主机实现嵌入式化。 本设计也是基于这种背景设计了一种支持高速和全速的嵌入式USB2. 0 主机控制器IP 核, 如图1 所示。

图1 嵌入式USB2. 0 主机控制器结构

2 主机控制器IP 核的设计

2. 1 主控制器

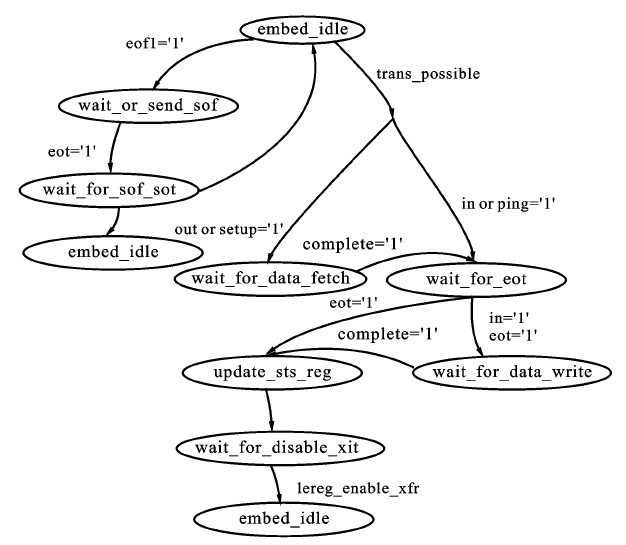

主控制器是整个USB 主机设计中的核心模块,它控制着嵌入USB 主机控制器中其它所有模块, 此模块主要采用一个总状态机来实现其控制作用, 如图2 所示。

图2 主控制状态机

其中每个状态下又有相应的子状态机。 当EOF1( end offrame1) 到来时, 将进入等待发送SOF( start offrame) 状态, 当传输数据有效时, 会有两种传输情况, 如果是OUT 传输或( setup) 配置时, 嵌入式主机读取存储器中数据, 数据读取完后会自动跳转到PIE 模块中的OUT 传输或setup 的子状态机来完成相应的具体操作并进入传输等待状态(waitfor eot) , 等待操作完成, 相应操作完成后, PIE 模块置EOT( end of transfer) 信号为1来宣告当前传输完成, 同时会更新状态寄存器中数据准备下一次操作。 当为IN 或ping 传输时, 与OUT 或setup 传输类似, 都会跳转到相关模块来完成相应的具体操作。

2. 2 配置寄存器

配置寄存器主要分为两种: 状态寄存器和控制寄存器。为了提高代码可读性, 设计中定义了5 个32 位寄存器: USB 命令寄存器; 端口状态寄存器;USB 信息包域A 寄存器; USB 信息包域B 寄存器;传输状态寄存器。 这些寄存器分别寄存数据传输中的一些控制命令, 传输状态, 端口状态改变情况以及传输数据包特性等。

2. 2. 1 DMA 控制器

本设计将DMA 控制器设计为两种工作模式:

DMAmaster模式和DMA slave 模式。 采用一个模式选择信号来选择DMA 工作模式, 如下:

此选择信号值由配置寄存器配置, 当总线没有外部DMA 控制器控制时, USB 主机中DMA 控制器选择工作在master 模式, 在这种模式中, 当USB主机有数据传输的需求时, DMA 控制器向CPU 发起请求, CPU 将对DMA 控制器配置数据传输的起始地址, 数据传输总大小, 传输数据包大小等信息,并释放总线给DMA 控制器接管, 此时DMA 控制器完全接管对总线的控制, USB 主机与存储器之间数据传输不经过CPU, 而直接交换USB 主机外部存储器和USB 主机内数据缓冲器之间数据。 当数据传输结束后DMA 控制器通知CPU 重新接管总线。

DMA master 模式一般用于高速地传送成组的数据。

DMA mater 模式的主要优点是速度快。 由于整个数据传输过程不需要CPU 干预, 因此就省去了CPU操作时间, 减少了CPU 工作负担, 减小了对CPU 的要求, 很大程度的降低成本。 当总线有外部DMA 控制器接管时, USB 主机中DMA 控制器工作在slave模式, 此时USB 主机内DMA 控制器模块不起作用, USB 主机与外部存储器之间数据传输必须经过CPU 来启动外部DMA 来搬运外部存储器和USB主机内数据缓冲器中的数据, 这样就加大了CPU 工作量, 对CPU 要求也相应的提高, 数据传输速度也有所下降。

2. 2. 2 数据缓冲器

数据缓冲器模块用来缓冲从设备端输入的数据和CPU 端要输出的数据。 本设计采用乒乓缓冲buffer0, buffer1, 在读buffer0 数据的同时在向buffer1 里写入下一个数据, 然后读buffer1 的数据并写数据到buffer0, 这样交替读写数据, 很大程度的提高了数据传输速度。 在IN 传输中, 将从设备端输入的数据写入数据缓冲器中, 数据写完后会发起一个中断信号通知CPU 来取出其中的数据, 同样在OUT 传输中, 将从CPU 过来的数据写入数据缓冲器中, 随后将写入的数据传输到设备端。

2. 2. 3 根集线器及PIE

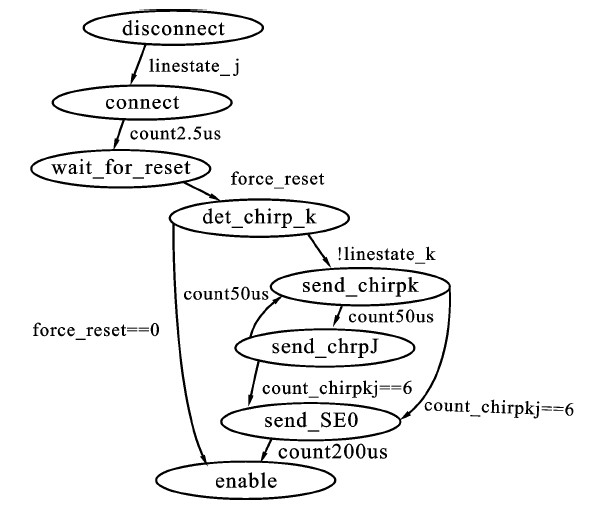

根集线器其实也是一种特殊的设备, 它下游端口还可以继续串联其他集线器, 最终能够为127 个USB 设备提供连接端口, 根集线器主要任务是管理连接到根集线器上的设备以及负责设备与主机之间的数据通信。 设计中通过图3 的状态机来实现根集线器对设备的枚举过程。

图3 枚举状态机

有高速能力的设备在第一次连接到USB 总线时必须使用全速。 而后, 该设备在总线重置阶段中向根集线器发送一个Chirp K, 如上游的集线器支持高速速率, 则应答一个Chirp K 与Chirp J 交替序列,这样高速集线器和高速设备都使用高速传输速率通信, 如根集线器不支持高速速率, 则忽略高速设备发送的Chirp K, 即不应答ChirpK 与Chirp J 交替序列。 这样高速设备必须维持在全速模式。

PIE 模块在设计中实现对传输的信息包处理,如包拆分, 包封装等。 其内部设计的子模块有crc. v,piddecoder. v, pid encoder. v, rec packet. v,trans packet. v, timeout. v 等等。 实现传输信息包中pid 的编码, 译码以及对pid 的检错等功能, 同时还包括对信息包的crc 检测及对数据传输过程中超时的检测。

3 系统验证环境

为了验证嵌入式USB2. 0 主机控制器, USB 接口用了PHY 模型和设备模型, 总线接口采用CPU和存储器模型, 如图4 所示, 外部CPU 和存储器有两个通道与嵌入式USB 主机作用: 寄存器通道和DMA通道。 CPU 通过寄存器通道来读写嵌入式USB 主机中配置寄存器中数据, 而DMA 通道主要用来交换存储器模型与嵌入式USB 主机中数据缓冲器中数据。

图4 嵌入式USB2. 0 主机控制器仿真环境

3. 1 CPU 模型

CPU 工作在12~ 160MHz 时钟频率。 CPU 模型通过读命令文件master. cmd 来触发嵌入式USB 主机开始配置寄存器的读写。

3. 2 存储器模型

在IN 传输中, 存储器模型通过DMA 通道从嵌入式USB 主机中数据缓冲器模块读出数据, 并将读出的数据写入data. dmp 文件中, 在OUT 传输中,嵌入式USB 主机通过DMA 通道读存储器模型中的数据到数据缓冲器, 而存储器模型中数据是存放在ehin. dat 文件中。

3. 3 PHY 模型

此处的PHY 模型包括USB 主机方的PHY1 和USB 设备方的PHY2, 本设计主要用于高速和全速的数据传输, 所以接入的PHY 模型为2. 0 版本。 它主要功能是串行数据与并行数据之间相互转换, 因为在嵌入式USB 主机中都为并行数据, 而在USB电缆中是以串行数据传输的。

3. 4 USB 设备模型

此模块通过读命令文件dev1. cmd 来控制USB信息包的发送与接收, 若IN 传输时设备模型将dev1 sen. dat 文件中所包含的数据发送给主机, 在OUT 传输中将主机输出的数据也储存在dev1rcv. dat 中。

为了方便观察仿真结果, 设计中还加入了一个验证传输中数据对错的模块, 在IN 传输中将设备模型中从dev1 sen. dat 发出的数据与USB 主机收到的数据进行对比, 在OUT 传输时将进入USB 主机的数据与设备模型中dev1 rcv. dat 收到的数据进行对比, 由此可以清楚的看出在USB 主机与设备之间是否正确传输数据。

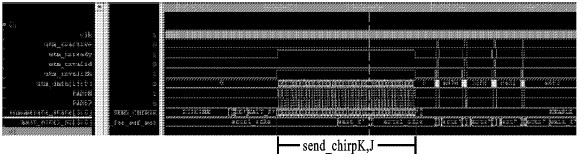

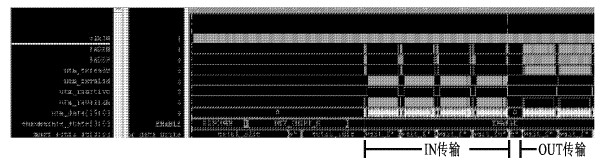

这里采用nc2verilog 分别对高速和全速中IN,OUT 传输以及枚举过程进行的功能仿真, 部分仿真波形如图5、图6 所示。 可以看到: 全速和高速的整个枚举过程中状态机enmumerate state 的变化直到传输使能; 整个主控制状态机mast ectrlst 中各状态的转换; 在每次数据传输中utmtxready, utm rxactive, utm rxvalid 以及utm rx2validh 的跳变过程。 在高速和全速的仿真中, 验证先IN 传输再OUT 传输, 即先从USB 设备模型中dev1sen. dat 文件中读出数据进行4 个信息包的IN 传输, 然后执行4 个信息包的OUT 传输。

图5 高速数据批量传输仿真图

图6 全速数据批量传输仿真图

4 FPGA 验证

FPGA 验证环境如图7 所示, 验证中外接一块USB2. 0 的PHY 子板和memory 子板, 其中FPGA芯片为Altara 公司的stratixIIs180, 其中实现嵌入式USB 主机IP 核和CPU 平台, memory 子板用来实现嵌入式软件, 在验证时分别接入支持高速和全速的U 盘作为设备, 对U 盘进行了数据的读写, 不管是在高速下还是在全速下都能正常完成U 盘的读写过程, 并与预期的读写数据一致。

图7 嵌入式USB2. 0 主机控制器验证环境

从nc2verilog 的功能仿真和FPGA 验证表明, 此嵌入式USB2. 0 主机控制器IP 核成功地实现了高速和全速下数据传输。

5 结束语

此嵌入式USB2. 0 主机控制器IP 核在设计中采用了乒乓缓冲模式提高了数据传输的速度, 还采用了DMA master 和slave 模式, 很大程度的减小了CPU 的要求, 在仿真和FPGA 验证中分别采用了CPU 频率为12MHz 和160MHz, 此IP 核都通过了功能验证。 目前已流片, 且通过芯片验证。 因此可以说此IP 核能够独立地用于数码相机, MP3 播放器里。 这样, 这些嵌入式的主机就可以直接和移动硬盘、打印机等设备连接用了, 不需要通过PC 机来进行相互的文件和数据交换, 实现了脱离PC 机的梦想, 方便了更多使用者。