摘要:文中介绍了一种低噪声的零中频放大器的设计与实现,通过选用合适的集成运算放大器芯片,完成低噪声、高增益并具备滤波效果的零中频放大器的设计。阐述了运放芯片的选择依据,电路的工作原理并使用Cadence制板软件完成了电路板的设计。实际测试结果表明,该电路工作稳定,噪声、增益、滤波特性等效果均很好。

近年来,随着技术进步和制作工艺的提高,零中频技术广泛应用在通信领域,并在其他领域的应用也逐步扩大。作为高增益的放大器,噪声的抑制设计特别重要,否则噪声经过放大后,再加上电路的本底噪声,信噪比将很差,同时也要避免运算放大器的自激,破坏自激条件。本文中介绍的零中频放大器是将150 kHz内微弱的微伏级信号进行放大,放大倍数为2 800倍,接近70 dB;加入了滤波电路,有效抑制地抑制了谐波;选用了合适的芯片和电路结果,使得整个系统噪声很小。

1 电路设计

1.1 系统总体设计方案

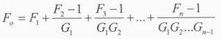

在进行系统设计的时候,首先得考虑增益的分配问题,这直接关系到整个系统最后的性能,也关系到芯片性能的选择与芯片使用的数量。式(1)为级联电路的噪声系数公式:

式中,Fi为第i级电路的噪声系数,Gi为第i级电路的额定功率增益。可以看出,各级内部噪声的影响并不相同,级数越靠前,对总的噪声系数的影响越大。所以,为了使整个零中频放大器的总噪声系数小,第一级和第二级选择的运算放大器要满足噪声系数小、增益高。在本设计中,把第一、二级分别作为低噪声放大器和低通滤波器。

为增强电路的抗干扰能力,使用差分线进行传输,这样做的好处主要有两点:1)可以进行远距离信号传输;2)对外部电磁干扰(EMI)是高度免疫的。在第二级信号输出端对其进行处理变成差分信号,这里有两种方法,一种是使信号通过一级同相放大与一级反相放大实现差分,另一种是直接使用单端转差分的芯片。在本设计中,鉴于方便性与可靠性,选择了后者。

最后,再用两个运算放大器对差分信号分别进行放大,同时增强其输出电流驱动能力。图1所示为整个零中频放大器电路的系统框图,并显示了每一级的电压放大倍数。

1.2 芯片选择与相应电路设计

芯片的选择主要由需要的性能指标决定,但满足要求的芯片一般都比较多,进一步的选择要考虑供电要求,这样便于统一供电,同时在系统前级的运算放大器压摆率要小于后级鉴于,此外.价格因素也不容忽视。

鉴于前两级的低噪高增益要求,选用了TI公司的OPA1612芯片,该芯片的电源供电范围很广,从±2.25 V到±18 V,压摆率为27V/μs,开环增益可达130 dB。噪声性能极好,为1.1n V/

。在100 Hz~150 kHz其等效输入噪声为1.1×

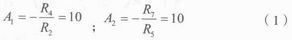

≈425.886nV,20 dB放大基础下,信噪比将非常好。图2为设计的前两级电路原理图,采用了多路反馈(MFB)结构,这种结构主要用于高增益的滤波器中。这种结构最大的好处是设计灵活,在制板的时候采用这种结构方便调试。第一级和第二级的放大倍数分别为:

图中R1的作用主要是为前级电路提供直流回路,C1是隔直电容。此外,电阻的选择要合理,过大会增加电路的热噪声,过小会使功耗提高。

在本文设计的零中频放大器中,单端转差分的设计方案采用ADA4941-1芯片,它可工作在±5 V,无需外部元件就能获得2倍增益,在实际设计的时候,考虑到增益分配的问题,加入了电阻反馈网络,获得4倍增益。该芯片的失真度也很小,达到了-110 dBc(100 kHz)。图3所示为ADA4941-1的工作原理图。输出电压为:

式中,VIN为前级的输出电压,VG为外部输入电压,VREF为连接到REF引脚上的电压,由式(2)和式(3)可知,输出共模电压为:

即输出共模电压即为连接到REF引脚上的电压。在本设计中VG=0,VREF=0,R8=1.1 kΩ,R10=3.3 kΩ,可知,输出共模电压为0,放大倍数为4倍,值得注意的是DIS为禁用管脚,在±5 V供电的时候DIS管脚上的电压要不大于-4 V才能使芯片工作。

最后一级主要是提高驱动能力并进一步提高增益,需要选用输出电流能力大的运算放大器。选用LMH6643,该芯片集成了两个运放,可分别为前面的差分信号提供服务,可用±5 V供电,线性输出电流达±75 mA,压摆率为130V/μs。图4给出了反相信号的放大电路原理图,正相信号与反相信号的工作原理一致,采用的也是多路反馈结构,放大倍数为7倍,R19=2 kΩ,这个电阻特别重要,不合适的值会引起信号的失真。

2 设计结果

原理图设计完成后就开始PCB的制作,使用Cadence公司的OrCAD软件画PCB板。由于零中频放大器前级通常是高频电路,为防止高频信号泄漏对其产生干扰,同时也为了安装方便,将零中频放大器电路板装配在金属盒中,设计的电路板为单面板,底层全为地。设汁的电路板尺寸为45 mm×25 mm。图5和图6为设计的PCB与实物图。

3 测试结果

对设计好的零中频放大器电路板进行焊接和装配,采用±8 V供电,经过7905和7805两款稳压芯片后得到-5 V和+5 V,为设计中用到的运算放大器芯片OPA1612,ADA4941-1,LMH6643进行供电。

图7(a)为输入信号峰峰值为2 mV,频率为50 kHz时的波形,其输出峰峰值为5.6 V,可得到该放大器的增益为68.9 dB;图7(b)给出了50 kHz时的频谱特性,其中在61 kHz处的频谱是由信号源本身自带的,与设计的系统无关;图7(c)显示了整个系统的滤波特性,其3 dB带宽约为150 kHz,由于设计中采用了巴特沃斯滤波器结构,在150 kHz内的频率响应曲线比较平滑,观察频谱幅度可以发现信号比噪声幅度至少大40 dB,抑制噪声效果良好;图7(d)显示了用ADA4941-1芯片来实现单端转差分的测试结果,可以看出,在4倍放大的情况下相位偏差与幅度偏差均非常小;图7(e)为测试信号不失真情况下最大可输出电压峰峰值为9.8V。从以上测试结果可以看出,设计效果良好,实现了低噪声、高增益的目标。

4 结论

文中主要阐述了一种低噪声零中频放大器的设计原理与实现,重点介绍了设计依据、芯片选择及其工作原理,并简单介绍了设计中该注意的问题。该系统目前已通过最终的测试,测试结果良好,实现了低噪声、高增益的设计目标。