摘要:基于Altera公司FPGA芯片EP2C8Q208,嵌入MC8051 IP Core,用C语言对MC8051 IP Core进行编程,以其作为控制核心,实现系统控制。在FPGA芯片中,利用Verilog HDL语言进行编程,设计了以MC8051 IP Core为核心的控制模块、计数模块、锁存模块和LCD显示模块等几部分,实现了频率的自动测量,测量范围为0.1Hz~50MHz,测量误差0.01%。并实现测频率、周期、占空比等功能。

关键词:FPGA;IP Core;等精度测频;LCD;VHD

频率是电信号中重要的物理量,在电子、通信系统中,信号的频率稳定度决定了整个系统的性能,准确测量信号的频率是系统设计的重要内容。

单片机广泛地应用于电子系统设计,其性价比高,大量的外围接口电路,使基于单片机的电子系统设计方便,周期缩短。然而,单片机的串行工作特点决定了它的低速性和程序跑飞,另外还存在抗干扰能力不强等缺点。EDA(Electronic Design Automation)技术以计算机为工具,在Quartus II软件平台上,对以硬件描述语言Verilog HDL/VHDL为系统逻辑描述手段完成的设计文件,自动地完成逻辑编译、化简、综合及优化、逻辑仿真,直至对特定目标芯片的适配、编译、逻辑映射和编程下载等工作,FPGA是纯硬件结构,具有较强的抗干扰能力。

文中在FPGA芯片中嵌入MC8051 IP Core,作为控制核心,利用Verilog HDL语言进行编程,设计了以MC8051 IPCore为核心的控制模块、计数模块、锁存模块和LCD显示模块等模块电路,采用等精度测量法,实现了频率的自动测量,测量范围为0.1 Hz~50 MHz,测量误差小于0.01%。

1 8051IP(Intelligent Property)软核

8051单片机是以由VQM原码(Verilog Quartus Mapping File)表达的,在QuartusII环境下能与VHDL、Verilog HDL等其他硬件描述语言混合编译综合,并在单片FPGA中实现全部硬件系统。

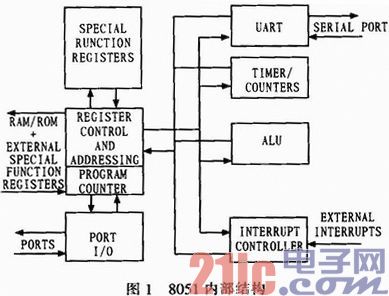

MC8051单片机核含有8位复杂指令CPU,存储器采用哈佛结构,其结构框图如图1所示。

MC8051的指令系统与8051/2、8031/2等完全兼容,硬件部分也基本相同,例如可接64KB外部存储器,可接256字节内部数据RAM,含两个16位定时/计数器,全双工串口,含节省功耗工作模式,中断响应结构等。不同之处主要有:

1)MC8051是以网表文件的方式存在的,只有通过编译综合,并载入FPGA中才以硬件的方式工作,而普通8051总是以硬件方式存在的;

2)MC8051无内部ROM和RAM,所有程序ROM和内部RAM都必须外接。

3)以软核方式存在能进行硬件修改和编辑;能对其进行仿真和嵌入式逻辑分析仪实现实时时序测试;能根据设计者的意愿将CPU、RAM、ROM、硬件功能模块和接口模块等实现于同一片FPGA中(即SOC)。

4)与普通8051不同,MC8051的4个I/O口是分开的。

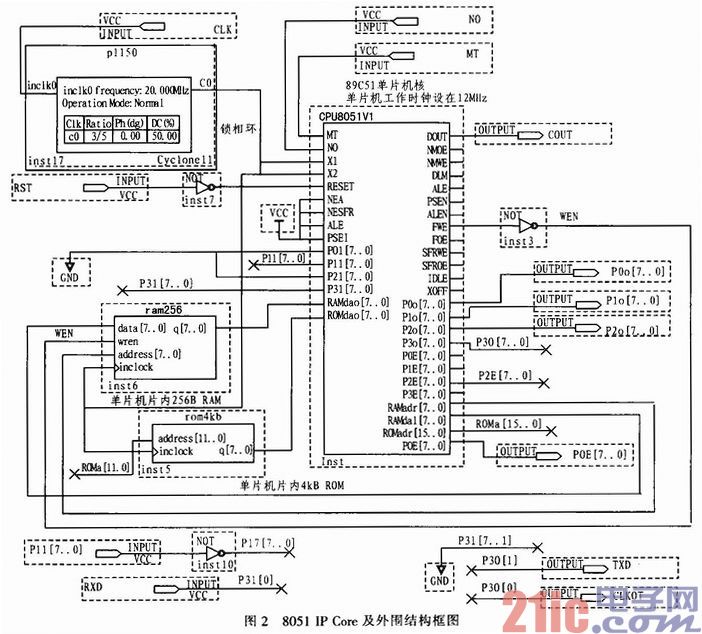

MC8051核在接上了ROM和RAM后就成为一个完整的8051或8052单片机了,MC8051核实用系统的最基本构建顶层原理图如图2所示,主要由4个部件构成。

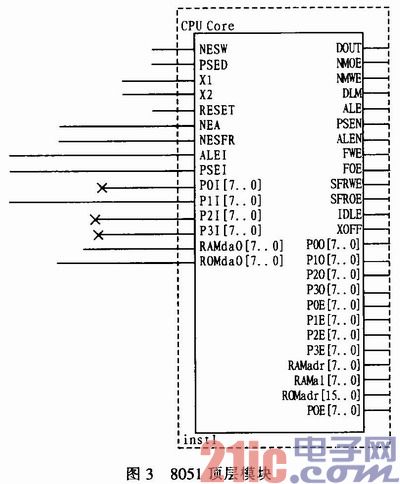

1)MC8051核。CPU_Core即MC8051单片机核如图3所示,由VQM原码表述:CPU_Core.vqm,可以直接凋用。该元件可以与其他不同语言表述的元件一同综合与编译。

2)嵌入式锁相环PLL50。其输入频率设置为50 MHz,MC8051能接受的工作时钟频率上限取决于FPCA的速度级别。

3)程序ROM,LPM_ROM。采用ROM容量的大小也取决于FPGA所含的嵌入RAM的大小。设置的ROM容量是4k字节。此ROM可以加载HEX格式文件作为单片机的程序代码。HEX程序代码可以直接使用普通8051单片机程序编译器生成。

4)数据RAM,LPM_RAM。本系统设置的LPM_RAM容量是256字节。高128字节须用间接寻址方式访问。

2 等精度测频原理及FPGA设计

等精度测量的一个最大特点是测量的实际门控时间不是一个固定值,而是一个与被测信号有关的值,刚好是被测信号的整数倍,即与被测信号同步。这样就达到了在整个测试频段的等精度测量。等精度测频的核心思想就是通过闸门的信号与被测信号同步,将闸门时间τ控制为被测信号周期长度的整数倍。测量时,先打开预置闸门,当检测到被测信号脉冲沿到达时,标准信号时钟开始计数。预置闸门关闭时,到达时才停止,完成被测信号整数个周期的测量。测量的实际闸门时间与预置闸门时间可能不完全相同,但最大差值不超过被测信号的一个周期。设实际闸门时间为τ,被测信号周期数为Nx,标准信号频率为fs、计数值为Ns,则被测信号的频率测量值为:

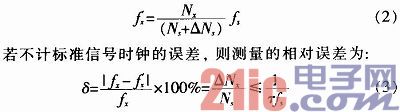

由于实际闸门时间τ为被测信号周期的整数倍,因此Nx是精确的,而标准信号时钟的计数值Ns则存在误差△Ns(|△Ns|≤1),即标准信号计数的真实值应Ns+△Ns。

由此可知被测信号的频率真实值为:

可以看出,相对误差与被测信号本身的频率特性无关,即对整个测量频率域而言,测量精度相等,因而称之为“等精度测量”。标准信号的计数值Ns越大,则测量相对误差越小,即提高门限时间τ和标准信号频率fs可以提高测量精度。在精度不变的情况下,提高标准信号频率可以缩短门限时间,提高测量速度。在计数允许时间内,同时对标准信号和被测信号进行计数,再通过数学公式推导得到被测信号的频率。由于门控信号是被测信号的整数倍,就消除了对被测信号产生的±1误差,但是会产生对标准信号±1的误差。如图4所示。

系统中,采用了标准信号源的精度很高,可以达到一个很高的测量精度,本系统采用晶体作为标准信号源,因此可以达到很高的精度。

3 FPAG设计模块

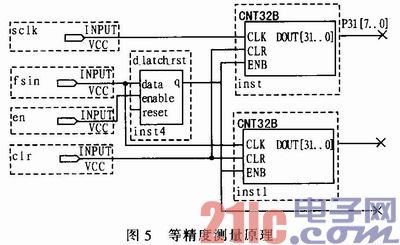

本系统以Verilog HDL硬件描述语言为工具,在传统的等精度测量原理基础上进行了改进和优化。增加了测量占空比的功能,同时由FPGA内部产生清零信号,节省了资源。FPGA核心模块如图5所示。FPGA部分主要由门控信号产生模块、计数器控制模块、计数器模块、锁存器、中断输出、数据选择输出、顶层模块组成。

门控信号:时钟信号源产生频率很高的时钟信号,经过分频以后,得到频率为1 Hz、1 kHz、1 MHz和50 MHz 4种时钟信号,这些信号作为时基电路输入信测量开始,TW为1s,计数器对被测信号fsin进行计数,如果计数超过规定值9999,产生溢出信号OVERFLOW,在其作用下,量程转换电路输出信号SW状态发生变化,自动完成一次量程的换挡,同时将TW调整为0.1s,计数器重新计数。如果还有溢出信号,继续量程换挡,调整TW,直到不再有溢出信号为止。其中74160接成了一个同步四进制加法计数器,如图6所示。它的时钟输入端CLK与计数器输出端OVERFLOW(溢出)连接,在溢出信号作用下,量程转换电路输出端S1、S0依次输出00、01、10和11 4个编码,实现自动换挡。

计数器控制模块:门控信号启动(上升沿)后,在被测信号的上升沿启动计数允许模块,允许计数器计数;门控信号关闭(下降沿)后,在被测信号的下一个上升沿关闭计数允许模块,停止计数,从而保证了门控信号是被测信号的整数倍,达到了等精度的目的。

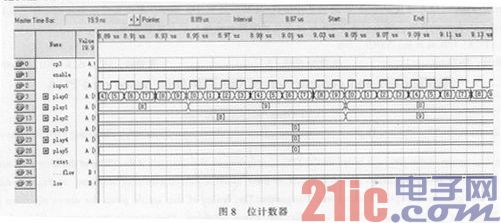

计数器模块:在设计计数器的过程中需要注意计数器的宽度设置,系统中采用的最大门控时间为10 s,标准信号源的频率为50 MHz,则在计数的允许时间内计数的最大值为:10 50 000 000=500 000 000<229=536 870 912,为了方便数据传输,系统中采用了32位位宽的计数,如图7所示,仿真波形如图8所示。

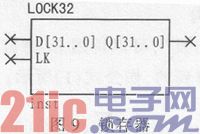

锁存器模块:在门控信号关闭的同时,停止计数,同时启动锁存模块,把测量的数据锁存起来,以便传输。

中断输出:锁存数据的同时,给单片机一个低电平的中断信号,通知单片机读取数据。该模块用于锁存计数器输出计数值,供51IP软核读取,进行处理显示。计数器模块在门控信号关闭(下降沿)的同时,停止计数,同时启动锁存模块,把测量的数据锁存起来,以便传输,锁存电路如图9所示。

数据选择输出:系统中采用了2个32位的计数器,由于单片机采用的是51系列单片机,只有8位的数据总线,所以一次通信只能传输8位数据,所以设计了一个数据输出控制模块。

顶层模块:实例化所有的底层模块。FPGA部分的整体结构图如图10所示。

4 MC8051 IP Core软件设计流程

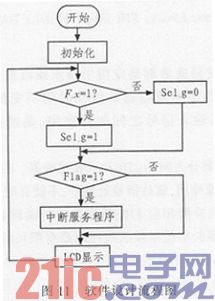

系统软件设计流程如图11所示。

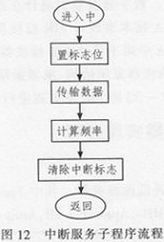

中断服务子程序如图12所示。

5 结论

文中采用Altera的cyclone II系列的EP2C8Q208C8这款FPGA芯片。设计中使用了Verilog语言对各个模块的描述设计。文中提出的数字频率计设计方案采用等精度的测量算法,以先进的FPGA可编程逻辑器件作为核心控制及运算电路单元可达到很高的测量精度要求,8051IPCore嵌入到FPGA芯片系统,与测频模块共用同一个FPGA芯片,和传统的频率计相比大大减小了电路板的尺寸,同时增加了系统的可靠性、设计灵活性和可更改性。实现了数字系统的软件化。加入LCD液晶显示,使测量效果更加直观。