前言

按照相对论的理论,时间也是可以被拉长缩短的,只不过需要巨大的能量支撑着您达到一个和光速可比拟的高速度而已。这话说着轻松,你我心里都明白,估计咱们的有生之年是看不到这样的情景的……

回到可编程逻辑器件领域,随着65nm、40nm,乃至目前的28nm深亚微米工艺的采用,厂家生产出了越来越大,也越来越复杂的FPGA器件。而用户们在为FPGA不断增强的功能和不断下降的单位成本而欣喜不已的同时,也在为相关EDA软件的性能滞后所带来的开发效率相对降低而苦恼不已,尤其是对大容量FPGA芯片动辄10到20个小时的编译时间可谓怨气冲天。笔者在许多次面对一线的FPGA工程师时,都听到了这样类似的话:要是编译时间能压一压就好了!

Altera不能真的压缩时间,但我们能改变“速度”!从数年前的版本开始,Quartus2软件中就整合了一种新技术,或者说一种新的设计流程:增量式编译(Incremental Compilation)。它是ALTERA为解决大容量FPGA设计编译时间太长的问题给出的一个新式工具!您,了解它吗?

增量式编译原理及流程

增量式编译QIC的原理很容易理解:对一个复杂的设计而言,肯定是需要做一定的功能划分,由不同的子功能模块来实现。那么在设计进入后期比较成熟的时候,前后两次编译的设计版本中,会有很大部分的电路逻辑都是相同的(没有修改),如果能在后一次编译中,重复利用前一次编译中未改变部分的编译结果,也就是相应部分的布局布线信息,那么就能把这部分逻辑所消耗的布局布线时间节约下来,从而在很大程度上缩短整个设计的编译时间。当然,聪明的读者都能想到,这样的编译方式,除了能缩短编译时间,还能支持许多别的用途,比如IP设计交付、团队开发、不改变正常设计结果插入调试接口等。这些确实都是ALTERA 增量式编译能够实现的功能,但在本文中我们只阐述QIC在缩短编译时间方面的作用。

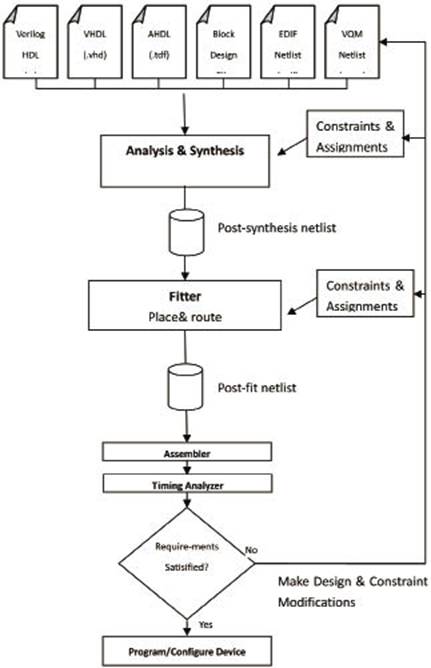

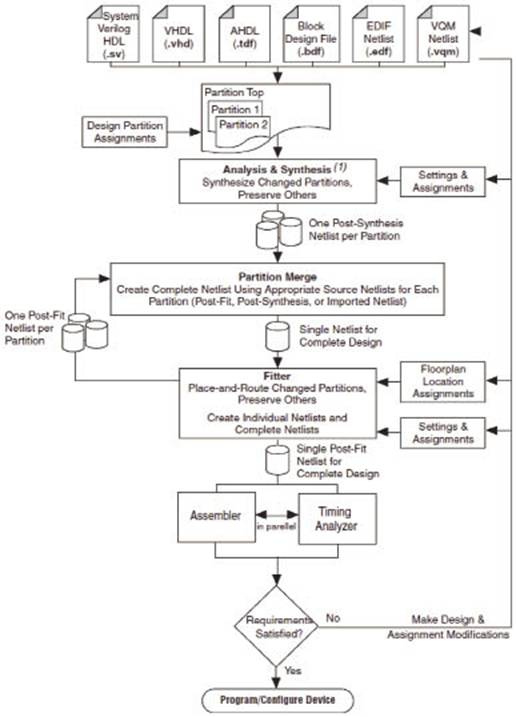

增量式编译原理虽然简单,但要在FPGA的EDA软件中实现,却是一个复杂的系统工程。它不是简单地在软件中增加一个功能模块,而是对编译处理流程多方面的改变和增强!请比较图1和图2两幅附图:图1是传统的FPGA编译流程(Altera名称:Flat compilation),图2则是增量式编译流程的示意图。我们很容易发现增量式编译流程复杂了许多,不仅引入了一些新的概念,比如设计分区(partition)、分区综合后网表、分区布局/布线后网表等,同时加入了新的处理阶段——分区合并(partition merging),而且对分析综合(Analysis&Synthesis)和布局布线(fitter)阶段进行了改进,增加了许多针对分区的具体操作。

<ignore_js_op>

图1 Flat Compilation 流程

<ignore_js_op>

图2 QIC增量式编译流程

经过几年的研究与实践,QuartusII的增量式编译已逐步完善,无论是在可操作性、稳健性方面,还是在缩短编译时间的效果方面,都十分出色。笔者参与的几个客户项目中,通过QIC的实施,都得到了50%左右的编译时间节约,极大提高了客户的开发效率。下面,我将结合这些实际项目中的经验,介绍如何实践利用QIC来高效的缩短设计编译时间。

QIC实践

QIC的效果评估

在讨论具体如何使用QIC之前,先考虑一个问题:如果读者在您的工作中使用了增量式编译QIC,怎么评估它的效能呢?

您需要至少做3轮实验,才能看到QIC节约编译时间的效果。首先,需要把您的设计用传统编译流程Flat Compilation进行编译,记录下各阶段所花费的时间。然后,创建合理的设计分区,指定分区网表性质,进行第二次编译,得到QIC各个分区的初始网表,并请记录下操作时间。第三次编译,您可以选择修改设计中的某一个分区,然后再编译一次,记录下操作花费的时间。将第三次的编译时间和第一次相比,正常的话应当看到非常明显的时间节约,这才是QIC增量式编译在编译时间节约方面的体现。

值得注意的是,第二次编译中已经使用了QIC,但往往花费时间和第一次编译差不多,有时还有增长。许多人为此怀疑QIC的性能,认为QIC没有效果甚至恶化了编译时间。这其实是一种误解!为什么呢?回到图2,我们可以看到,QIC流程在Analysis&Synthesis和fitter之间增加了一个新的处理阶段——分区合并,它是需要额外花费在第一次Flat Compilation中不存在的时间。而且,由于这是创建分区后的第一次编译,所有分区的网表都是空白的,也就是说整个设计都需要被编译、分析、综合、布局布线等的工作量和第一次编译是类似的,因此这部分花费的时间也是差不多。把这两部分时间加起来,自然第2次编译时间有可能会比第一次长了。只有当进行第3次编译的时候,各个分区都有可重用的网表了,才有可能将那些没有设计改变的分区的网表重用,从而节约综合和布局布线阶段的时间,达到整体编译时间的节约。

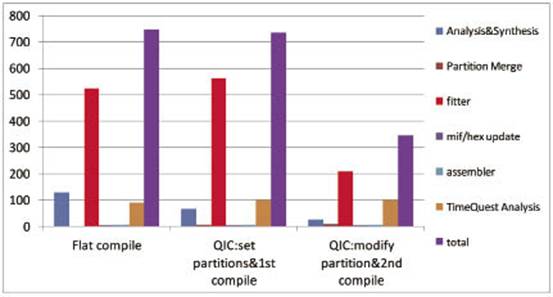

图3是笔者支持的一个客户所进行的QIC增量式编译性能评估的结果总结。客户的设计是高端路由器中的包处理应用,使用了ALTERA公司的Stratix4GX530器件,逻辑利用率大约是60%。客户的编译硬件是一台高性能服务器:、

<ignore_js_op>

图3 Z客户增量式编译评估实验效果

• CPU:16core Intel(R) Xeon(R) CPU E7420 @2.13GHz

• Memory:64GB

即使是如此,在不使用QIC的情况下,客户的每次编译都需要12到13个小时。而在使用QIC并根据QIC指导原则进行了必要的设计优化后,最好的实验结果是可以在6个小时左右(大约350分钟)完成一次编译,节约了接近55%的总编译时间!从图3中很容易看出前面文字描述的几个特点:

1. 第一次编译和第二次编译的总时间差不多(750 VS 730)

2. 第三次编译中,Analysis&Synthesis操作的时间,fitter操作得时间都比第一次编译有非常明显的降低;

3. 从原理上看,QIC的网表重用对Assembly和时序分析没有直接影响。因此三次编译中,Assembler和时序分析所花费的时间是差不多的。

QIC指导原则

合理创建分区

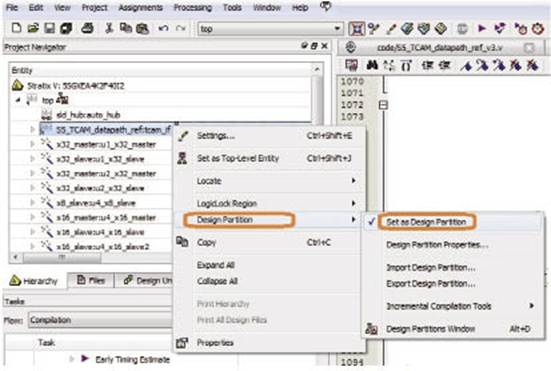

Quartus中的“分区”是和设计层次紧密关联的。任何设计,无论简单还是复杂,都会有一个顶层模块(top-level module),Quartus自动将它设置为一个默认分区(命名为top),不需要用户设定。而别的分区,需要用户手动创建。创建分区的方法很简单,在Quartus GUI界面左上角的Hierarchy窗口,选择想创建分区的实体,右键唤出的菜单中选择“Design Partition”,然后在下一级菜单中选择”Setting as Design Partition”,分区就创建成功了。

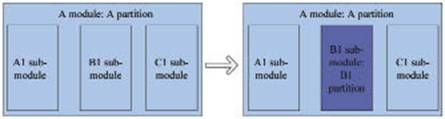

从图2可以看出,分区(Partition)是增量式编译中的一个关键概念。Altera规定:只要是有完整设计边界的设计实体,无论它在设计的哪一层次,都可以用它来创建设计分区。也就是说,Quartus II中,设计中任何层次中的任何一个设计模块,可以作为一个设计分区;一个设计中也可以包含不止一个设计分区;即使是在设计的同一层次,也可有多个分区。同时,请注意:分区之间没有层次关系,任何逻辑只能归属于某一个分区。以图5为例,A模块由A1、B1、C1三个子模块组成。如果A模块被设置为分区,Quartus会用模块名来为此分区命名:A分区。那么,A分区中就会包含A1、B1、C1三个子模块的所有逻辑。但如果把B1子模块也创建为分区,那么,A分区中就只包含A1、C1两个子模块的逻辑,B1子模块的逻辑只属于新的B1分区了。

图4 在Quartus GUI中创建分区示意

<ignore_js_op>

图5 分区与逻辑归属变化

<ignore_js_op>

图6 分区合并报告

<ignore_js_op>

图7 分区综合后资源使用统计

<ignore_js_op>

图8 Design partition window

<ignore_js_op>

图9 Design partition window

从前面分区的性质和特点可以看出,对包含多个功能模块的多层次复杂设计,可以有许多种设置分区的方案。但需要注意的是:不是任何一种分区方案都能带来编译时间的节约,恶劣的设计分区甚至能够导致编译失败!如何得到高效合理的设计分区呢?我们需要遵从以下原则:

a. 不要创建太多的分区,一般性的设计建议分区的数量控制在4~8个之间;

b. 不要创建太小的分区,一般建议不要小于1000个LE或者ALM;

c. 外设接口逻辑和内核处理逻辑放到不同的设计分区;

d. 相同或相近功能的外设接口,如果管脚位置相邻,可以放在同一个分区,否则创建不同的设计分区;

e. 不同的分区方案中,分区之间的联接少的方案更优。

针对QIC优化代码

除了分区方案,设计代码也对QIC的性能有直接的影响,需要设计者针对QIC做一些特定的代码优化。优化主要有两方面,一方面是升级所使用的Megacore IP到最新的版本;另一方面则是一些更严格的编码规则。

之所以建议升级Megacore IP到最新的版本,这是由于QIC增量式编译常常需要调用Megacore IP的一些特性来支持一些特定操作,而这些特性通常在较新的版本中才能得到比较好的支持,而且随着QIC的成熟不断改进。笔者就曾经在一个尝试使用QIC的项目中,发现客户的设计继承了一部分老项目中的代码,其中包含好几个Quartus 9.1版本的DDR EMIF控制器,占了整个设计使用资源的20%左右。当说服客户把这几个控制器升级到当时最新的Quartus 11版本,发现QIC所能节约的编译时间增加了近1个小时,大约15%的整体编译时间。

之所以QIC要求遵从更严格的编码规则,这是由于Quartus在有分区存在的时候,是不对跨越分区边界的逻辑进行综合优化,一些在Flat compilation中可以被软件优化掉的不良代码,在QIC的流程中会造成严重的影响。这些严格的编码规则包括:

a. 不要在底层分区边界上使用三态信号和双向端口;

Altera器件中,只有在器件的输出管脚上才能实现真正的三态信号,在器件内部,三态驱动是依靠多路器逻辑模拟实现,这两点往往要求跨层的编译优化,而这在增量式编译流程中是做不到的,会导致编译失败。只有一种情形例外,就是内部三态逻辑所涉及的所有信号都在同一个底层分区中,Quartus可以依靠多路器逻辑模拟此三态逻辑。双向端口也类似,只有在此双向逻辑所涉及的所有信号都在一个底层分区中,QIC才能正常进行。

b. 分区的输入输出最好都通过寄存器实现,资源有限的情况下至少保证跨分区的连接中的一端是寄存器(reg-in或者reg-out);

虽然这一规则有一定的实现难度,但它可以避免在使用增量式编译流程的时候,那些跨分区边界的信号的延迟出现大的恶化。如果不能实现这一规则,跨分区连接的两端有可能都是组合逻辑。在Flat Compilation中,这两组组合逻辑会被综合优化到一起来布局布线,时序容易满足;但在是增量式编译中,由于不能跨区优化,这2组组合逻辑的分别布局布线,那穿过这两组逻辑的路径延迟将有可能变得很长,出现时序违背。

c. 避免不包含任何处理逻辑的信号环路穿越分区边界;

也是由于不能跨区优化,这样的信号环在Flat Compilation中可以被优化消除掉,在增量式编译中就不能消除,浪费资源。

d. 避免跨分区的常量信号

类似C,跨区的常量信号不能在目的端分区中直接实现(“0”连接地层,“1”连接电源层),而必须占用走线资源实现。

关注相关报告信息

使用QIC时,Quartus中会产生很多QIC专有的消息,因此在编译报告中也增加一些新的章节。这些报告章节,对我们了解QIC的运行情况有直接的帮助,尤其是当一些异常情况出现,往往需要我们通过阅读这些报告章节来进行调试。比较重要的报告有:

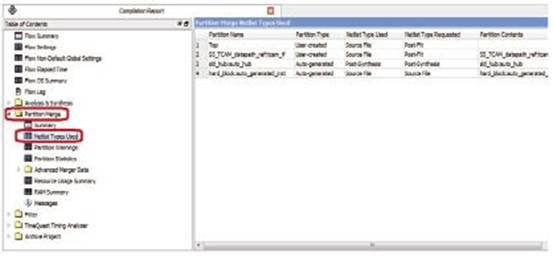

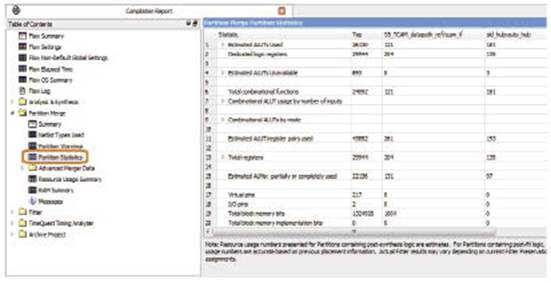

a. Partition Merge report

分区合并的报告章节如下图所示,分别提供在这个阶段网表的使用情况(netlist Types Used),各个分区的综合警告信息(Partition Warning)和综合后各类资源使用情况(Partition Statistics)。

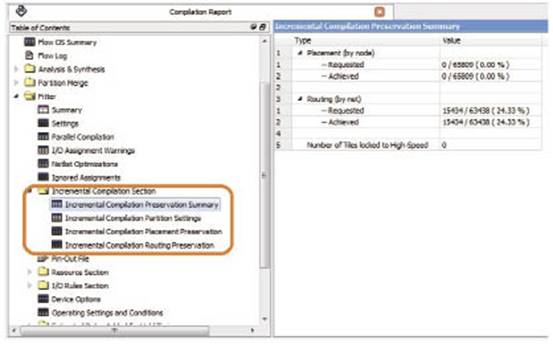

b. Incremental compilation section in Fitter report

在Fitter报告中,也增加了增量式编译的章节。其中,Incremental Compilation Preservation Summary汇总了设计中被保留的布局和布线比例;Incremental Compilation Partition setting 说明了设计中所有分区的创建方式和网表的保留级别(Preservation level);Incremental Compilation Placement Preservation给出了每一个分区中节点保留的信息;Incremental Compilation Routing Preservation则是每个分区中布线保留的信息。

c. Design partition window

这个窗口默认是不在Quartus 界面中显示的,用户需要通过Quartus菜单栏“Assignments”->”Design partition window”打开这个窗口。这个窗口给出可配置分区的当前设置及各个网表文件的时间戳信息,并且可以在此窗口中快速修改分区使用的网表类型(Netlist Type)和Fitter网表的保留级别(Fitter Preservation Level)。

结束语

在本文中,向大家介绍了增量式编译的原理、过程和一些性能表现,同时给出了使用QIC需要注意的一些指导原则。华为、中兴等客户的多个项目实践已经证明QIC是一个可以用来解决大容量FPGA设计编译时间太长的有效手段。增量式编译QIC,值得您去尝试!