基于FPGA的通用位同步器设计方案(二).doc

时间:09-23 13:49

查看:908次

下载:162次

简介:

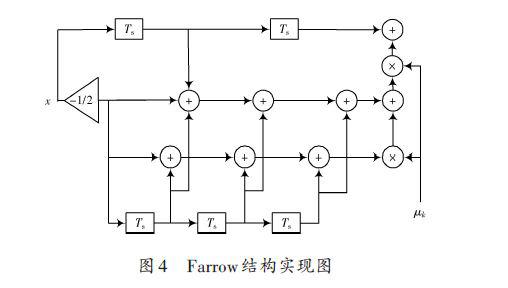

本文提出了一种基于FPGA的通用位同步器设计方案。方案中的同步器是采用改进后的Gardner算法结构,其中,内插滤波器采用系数实时计算的Farrow结构,定时误差检测采用独立于载波相位偏差的GA-TED算法,内部控制器和环路滤波器的参数可由外部控制器设置,因而可以适应较宽速率范围内的基带码元。

本文提出了一种基于FPGA的通用位同步器设计方案。方案中的同步器是采用改进后的Gardner算法结构,其中,内插滤波器采用系数实时计算的Farrow结构,定时误差检测采用独立于载波相位偏差的GA-TED算法,内部控制器和环路滤波器的参数可由外部控制器设置,因而可以适应较宽速率范围内的基带码元。

本文主要是先阐述传统Gardner算法的原理,然后给出改进后的设计和FPGA实现方法,最后对结果进行仿真和分析,证明该设计方案的正确、可行性。