基于FPGA的数字钟设计-大学毕业论文.doc

时间:11-03 12:17

查看:1220次

下载:162次

简介:

本设计为一个多功能的数字钟,具有年、月、日、时、分、秒计数显示功能,以24小时循环计数;具有校对功能以及整点报时功能。

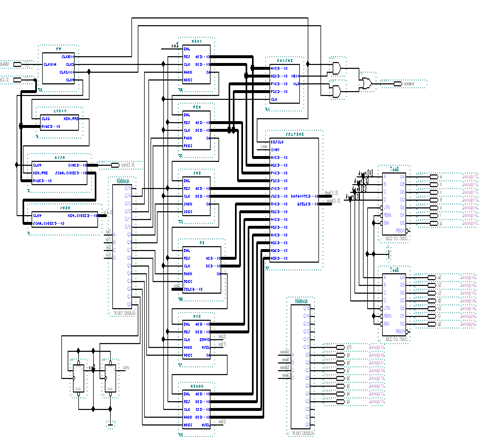

本设计采用EDA技术,以硬件描述语言VHDL为系统逻辑描述手段设计文件,在MaxplusII工具软件环境下,采用自顶向下的设计方法,由各个基本模块共同构建了一个基于FPGA的数字钟。

系统主芯片采用EP1K100QC208-3,由时钟模块、控制模块、计时模块、数据译码模块、显示以及报时模块组成。经编译和仿真所设计的程序,在可编程逻辑器件上下载验证,本系统能够完成年、月、日和时、分、秒的分别显示,由按键输入进行数字钟的校时、清零、启停功能。