基于FPGA的幅值可调信号发生器设计

时间:11-25 10:53

查看:794次

下载:162次

简介:

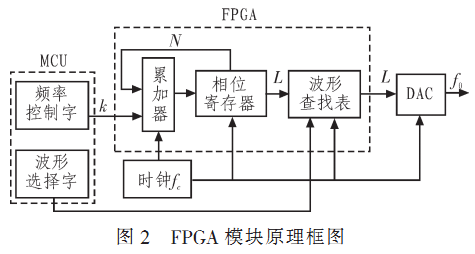

针对信号发生器对输出频率精度高和幅值可调的要求,采用直接数字频率合成(DDS)技术,提出一种基于FPGA的幅值、频率均可调的、高分辨率、高稳定度的信号发生器设计方案。采用AT89S52单片机为控制器,控制FPGA产生波形的数字信号,结合双数模(D/A)转换器及低通滤波器,最终实现输出信号幅值0~5 V可调,分辨率为10 bits;频率范围1 Hz~10 MHz可调,最小分辨率为1 Hz;频率稳定度优于10-4。信号参数可通过键盘进行设置,并在LCD上输出。由于FPGA的可编程性,易于对系统进行升级和优化。