基于HMC830的低相噪低杂散频率源的设计

时间:11-28 13:46

查看:1480次

下载:162次

简介:

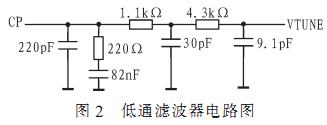

针对频率源的相噪会恶化采样数据的信噪比,杂散会降低接收机灵敏度,提出了一种低相噪低杂散的设计方法。该方法利用Hittite公司的新推出的集成VCO的锁相环芯片HMC830进行设计,供电部分采用多个低噪声稳压芯片,参考频率源为Pascall公司的OCXO晶振,环路滤波器为无源四阶,使用Hittite PLL Design软件进行设计,另外采用C8051F300单片机对锁相环芯片进行寄存器操作。实验结果显示:鉴相频率为100 MHz,输出频率为1.8 GHz时,整数分频模式下,相位噪声为-112.2 dBc/Hz@1 kHz,杂散抑制度为-75.6 dBc。