基于FPGA的DDS IP核设计

时间:12-05 10:46

查看:3125次

下载:162次

简介:

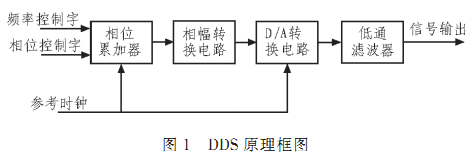

以Altera公司的Quartus Ⅱ 7.2作为开发工具,研究了基于FPGA的DDS IP核设计,并给出基于Signal Tap II嵌入式逻辑分析仪的仿真测试结果。将设计的DDS IP核封装成为SOPC Builder自定义的组件,结合32位嵌入式CPU软核Nios II,构成可编程片上系统(SOPC),利用极少的硬件资源实现了可重构信号源。该系统基本功能都在FPGA芯片内完成,利用 SOPC技术,在一片 FPGA 芯片上实现了整个信号源的硬件开发平台,达到既简化电路设计、又提高系统稳定性和可靠性的目的。