基于FPGA的DDC设计及仿真

时间:12-11 13:47

查看:1437次

下载:162次

简介:

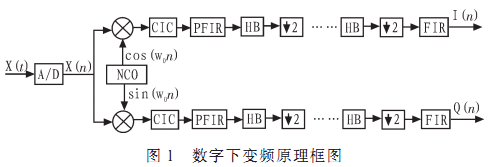

在软件无线电数字接收机中,从AD前端采集过来的数字信号频率高达72 MHz,如此高的频率使得后端DSP不能直接完成相关的数字信号处理任务。因此合理的设计基于FPGA的DDC,以降低数字信号频率,方便后端DSP实时完成相关的数字信号处理任务就显得尤为重要。在很多数字信号处理系统中,数字信号频率是非常高的,而后端数字信号处理器件几乎不能满足系统的实时性要求,此时通过合理的设计DDC就可以解决上述问题。