FPGA实现的任意波形发生器的设计.pdf

时间:01-16 09:05

查看:1780次

下载:163次

简介:

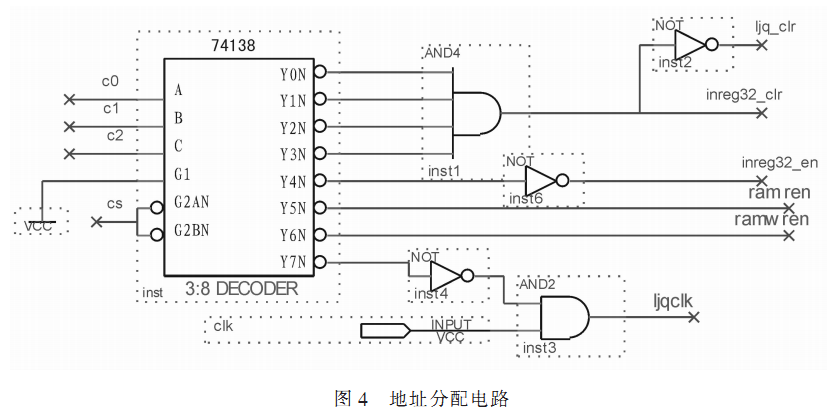

运用DDS原理,进行任意波形发生器的设计,使得任意波形发生器兼顾DDS的优点。设计中通过实现DDS模块与单片机接口的控制部分将频率控制字由单片输入到输入寄存器模块,由相位累加器模块对输入频率控制字进行累加运算,输出作为双口RAM的读地址线,读数据线上即输出了波形幅度量化数据。其中双口RAM的内容由单片机进行更新,从而实现任意波形的发生。本设计中的相位累加器采用了8级流水线结构借助前5级的超前进位的方法,使得编译的最高工作频率由317.97 MHz提高到336.7 MHz, 实现了任意波形的发生,节约了成本,提高了开发周期,具有可行性。