一种开环高速高精度采样保持电路.pdf

时间:03-17 11:06

查看:1471次

下载:163次

简介:

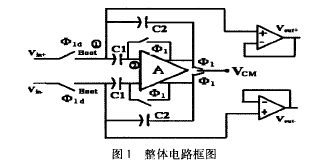

设计了一种改进型开环结构采样保持电路。与传统M川er电容开环结构相比,本设计采用了新型Bootsrapped开关,不但实现了沟道导通电阻线性化,而且消除了与输入信号相关的时钟馈通;采用全差分结构消除了共模信号引入的误差以及偶阶谐波,提高了电路的信噪比;采用高速高精度缓冲器增大电路的驱动能力,实现了高速高精度采样。设计采用O.35 m n—welI cMOS工艺,经仿真验证,在驱动2.5pF负载电容下采样率达到10OMsPS,电路有效位数l2bits,功耗为21.5mW 。