FPGA的电源定序电路.pdf

时间:04-02 14:36

查看:1124次

下载:162次

简介:

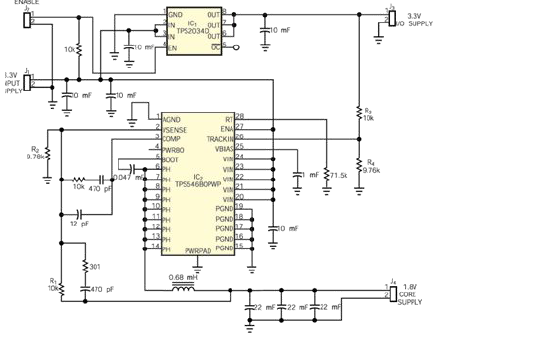

系统设计师必须考虑加电和断电期间芯核电源和I/O 源之间的定时差和电压差(换言之,就是电源定序)问题。当电源定序不当时,就有可能发生闭锁失灵或电流消耗过大的现象。如果两个电源加到芯核接口和I/O 接口上的电位不同时,就会出现触发闭锁。定序要求不相同的FPGA 和其他元件会使电源系统设计更加复杂化。为了排除定序问题,你应当在加电和断电期间使芯核电源和I/O 电源之间的电压差最小。图1 所示的电源将3.3V 输入电压调节到1.8V 芯核电压,并在加电和断电期间跟踪3.3V I/O 电压,以使两电源线之间的电压差最小。