FPGA的IPV6数字包分离与封装电路设计.pdf

时间:04-03 14:17

查看:1364次

下载:162次

简介:

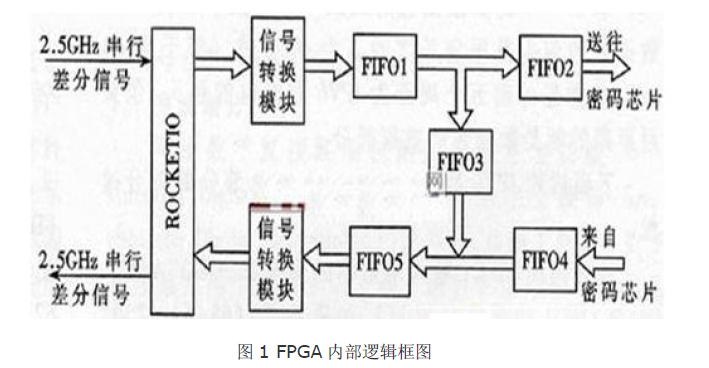

笔者在参加国家“863”重大专题项目“高速密码芯片及验证平台系统”的过程中,遇到了将IPV6数据包的包头和数据部分拆开,然后在数据部分送密码芯片进行加/解密处理,最后再将处理后的数据部分与包头重新封装为数据包的课题。以往对IP包进行拆装多利用软件实现,但本项目涉及到配合高速密码芯片(处理速度在2Gbit/s以上)工作的问题,显然利用软件实现IP包的拆装在速度上达不到要求。为此,笔者运用FPGA(型号为Xilinx公司的XC2VP20-FF86CGB0345)来实现IPV6数据包的拆装。该FPGA内部逻辑框图如图1所示。