在verilog程序设计中,我们往往要对一个频率进行任意分频,而且占空比也有一定的要求。这样的话,对于程序就会有一定的要求,本篇文章将在前人经验的基础上做一个简单的总结,实现对一个频率的任意占空比以及任意分频的确定。

比如:我们FPGA系统时钟是50M Hz,而我们要产生的频率是880Hz,那么,我们需要对系统时钟进行分频。我们很容易想到用计数的方式来分频:

50000000/880 = 56818

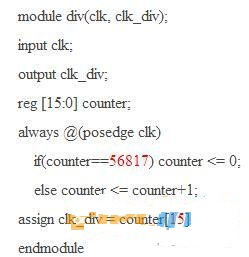

这个数字不是2的整幂次方,那么怎么办呢?我们可以设定一个参数,让它到56818的时候重新计数不就完了吗?程序如下:

在我们日常的设计中很多情形下会用到需要分频的情形,好多人的做法是先用高频时钟计数,然后使用计数器的某一位输出作为工作时钟,进行其他的逻辑设计,上面的程序就是一个体现。

下面我们来算一下它的占空比:我们清楚地知道,这个输出波形在counter为0到32767的时候表现为低,在32768到56817的时候为高,占空比为40%多一些,如果我们需要占空比为50%,那么怎么办呢?

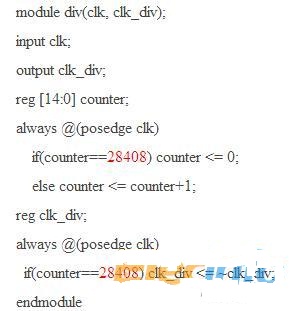

我们再设定一个参数,使它为56817的一半,使达到它的时候波形翻转:

占空比是不是神奇地变成50%了呢?

继续让我们来看如何实现任意占空比,比如还是由50 M 分频产生880 Hz,而分频得到的信号的占空比为30%。

56818×30%=17045

本篇文章介绍了一种在Verilog当中确定占空比和分频的方法,并给出了计算公式与相关代码。占空比越高,就代表着电能的利用率越高,所以占空比的决定往往与一个电路的性能有着密切的关系。希望大家通过本篇文章能够学会这种占空比的确定方法,从而加速自己的设计。