晶体谐振器是生成微机(微型计算机)等的集成电路的基准时钟信号的重要部件之一,从手机、智能手机等信息通信终端到汽车、日用家电,用途非常广泛。其中特别是在信息通信终端用途上,对部件小型化的需求很强,从而给部件设计带来了难题—维持产品特性的同时还要缩小其体积。我们在这里介绍一种方法,它的核心是应用了有限元法 (FEM) 的模拟技法,通过对其进行灵活运用,可以有效率地开展设计工作。

1. AT切割晶体谐振器与振荡电路

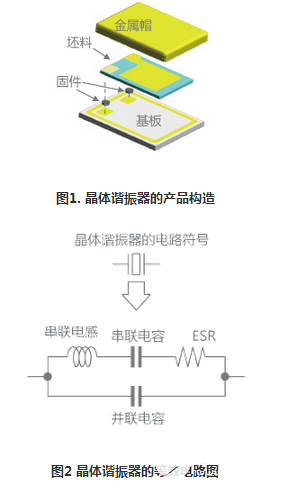

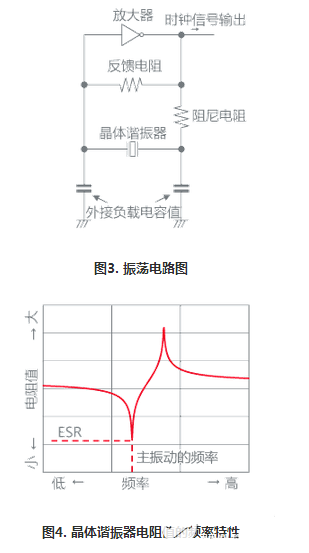

AT切割晶体谐振器是以人工石英晶体为材料、利用了压电特性(厚度剪切振动)的元件。我们将村田的代表性产品构造用图1、等效电路用图2来表示。此元件是构成发出让微机工作时必要的基准时钟信号的振荡电路的重要部件之一。此外,我们将振荡电路的代表性构造用图3来表示。振荡电路借助放大器将通过晶体谐振器的电气信号增幅而发出时钟信号。晶体谐振器如图4所示,电阻值会根据频率而变化。此时坯料(晶体坯)的主振动频率电阻值为最小,这个电阻值叫做ESR 。振荡电路在坯料的主振动频率附近振荡并输出时钟信号。

振荡电路重要的一点是振荡稳定。其指标之一是振荡裕量 ,显示对于ESR(信号衰减的重要原因),电路中晶体谐振器以外的部分有多大的信号增幅能力。理论上,振荡裕量>1,电路就会振荡,但偶尔会出现在接近1倍时不振荡、振荡启动时间异常地长等现象,导致电路所在设备不能正常工作。抑制ESR可以改善振荡裕量,但通常在频率越低时ESR就越高,而且产品尺寸越小时ESR也越高。信息终端等现在使用的是2016和1612尺寸的产品,而市场需求的是更小型,所以近来设计变得很不容易。

2. 特性设计的要点

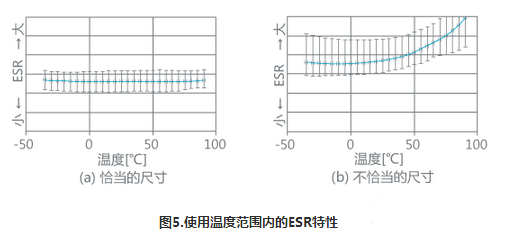

除作为主振动使用的厚度剪切振动以外,AT切割晶体谐振器还存在着很多不必要的振动。设计晶体谐振器时,需要一边考虑如何在使用温度范围内不让这些不必要的振动影响工作,一边决定几何参数。图5显示的是温度和ESR的关系,对选择了恰当几何形状的设计(a)和选择了不恰当几何形状的设计(b)的特性进行比较。选择了不恰当的几何参数时,不必要的振动会叠加,ESR值会增大。在设计阶段,选择不受不必要振动影响的几何参数是关键。但是,几何参数组合的数目庞大,很多时候为找出最优解要反复地实验摸索,这已经成为阻碍缩短开发期间和难以提高品质的原因之一。

3. 模拟(有限元法: FEM)的应用与课题

作为高效地找出最优解的手段,可以考虑应用有限元法(FEM)进行特性模拟。但是,这种方法存在一个问题,就是模拟结果和实样特性的一致性较低。我们已经找到了其原因—不仅是几何形状,连接坯料与基板的固件也会给主振动(厚度剪切振动)和不必要振动的频率关系带来很大影响。

图6显示不考虑在基板上的固件只将坯料模化时的FEM模拟结果与实样特性的对比。模拟无固件形状的结果中,ESR特性的倾向与实样特性不一致,无法找出恰当的几何参数。

如上所示,确立模拟技法以提高模拟结果与样本特性的一致性、有效率地寻求最优解一直是我们的课题。而这次通过构建能解决这些课题的模拟体系,我们已经能够提高模拟结果与实样特性的一致性了。