SDRAM即同步动态随机存储器(Synchronous Dynamic Random Access Memory)。由于其大容量、价格优廉、无需等待时间等优点在早期的PC机种得到了广泛的应用。不同于其他的FLASH、SRAM和MRAM等存储器,SDRAM需要同步时钟,并且每隔一段时间需要刷新,否则数据将丢失。由于其功能强大、时序复杂,往往给应用者带来极大地困难。本应用案例基于珠海欧比特控制工程股份有限公司的立体封装大容量VDSD3G48芯片,介绍了对应的SDRAM控制器在FPGA上的实现,探讨其使用方法。

1、VDSD3G48芯片介绍

VDSD3G48是一款容量3072M bits SDRAM 。它采用先进的立体封装技术,由六片容量为8M×16×4banks的基片堆叠而成,组成了容量为32M×48×2的48位宽的数据接口存储器。六片基片都有一个独立的片选信号,通过两组片选信号#CS0、#CS2、#CS4和#CS1、#CS3、#CS5可选择具有48位宽的不同的存储阵列。另外,通过六个片选信号和配合DQMH和LDQL信号可有选择的选择哪片基片工作和选择输出每片基片16位的高低8位,组成8、16、32、48位宽的存储器。通过应用了立体封装的技术缩短了互连导线,从而降低了寄生效应,使得器件具有高性能、高可靠、长寿命、大容量等的性能特点。

1.1 芯片的内部功能结构和外部引脚

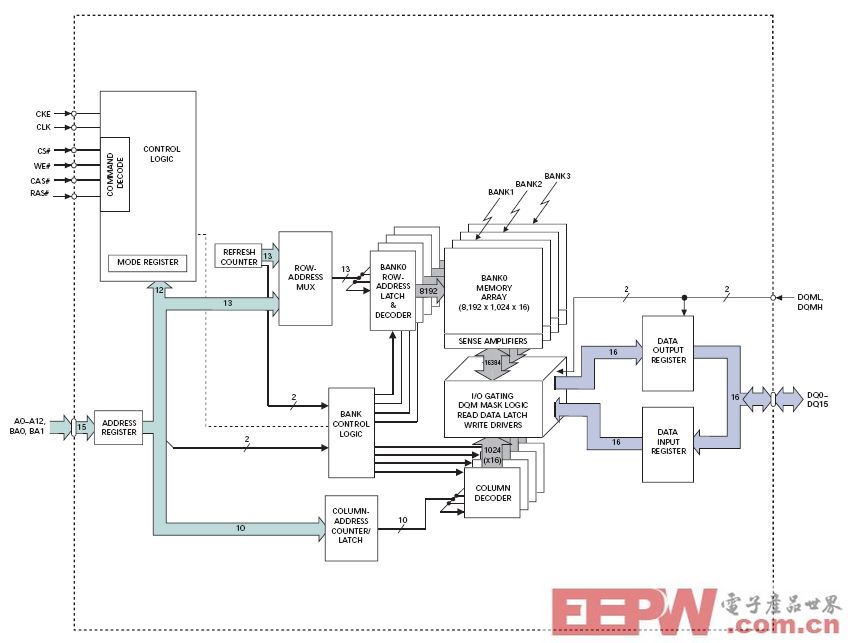

图1是立体封装的大容量芯片VDSD3G48中每一片基片的内部结构和功能框图,由MEMORY存储阵列、控制逻辑(包括指令译码和模式寄存器等)、列地址译码器、列地址锁存器、bank控制逻辑、行地址数据选择器、bank行地址锁存器、刷新定时器、读数据锁存和屏蔽和输出数据寄存器等部分组成。

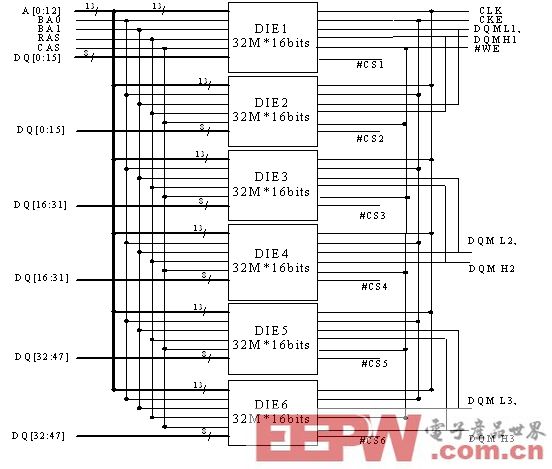

图2是立体封装的大容量存储芯片VDSD3G48的内部结构和功能框图,其中A[0:12]为地址线,BA0、BA1是banks选择信号、CLK是时钟输入信号,#CS0-#CS5是六片基片DIE1-DIE6的芯片片选信号,CKE、RAS、CAS、WE 是控制信号,DQ[0:47]是芯片的数据线,其中数据线DQ[0:15]为DIE1、DIE2的数据线,数据线DQ[16:31]为DIE3、 DIE4的数据线,数据线DQ[32:47]为DIE4、DIE5数据线,DQMH0 、DQMH1、DQMH2、DQMH3 、DQMH4、DQMH5和DQML0 、DQML1、DQML2、DQML3 、DQML4、DQML5分别为DIE1-DIE6的高低8位的输出屏蔽信号。

图1 VDSD3G48中基片的的内部功能结构框图

图2 VDSD3G48的功能总结构框图

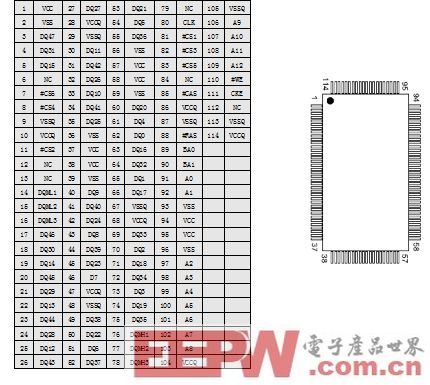

VDSD3G48引脚的功能如表1所示:

表1 VDSD3G48引脚功能说明

1.2 芯片的主要特性

1、3.3V+0.3V电源电压;

2、时钟频率高达133MHz;

3、完全同步:所有信号在时钟的上升沿锁存;

4、内部流水线操作;

5、可编程爆发长度:1,2,4,8或页;

6、自动预充电;

7、自动刷新;

8、64ms,8192-刷新周期;

9、兼容LVTTL;

1.3 芯片的操作

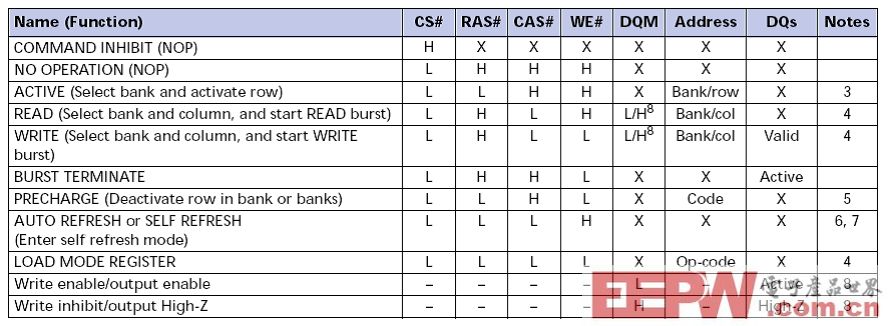

芯片VDSD3G48操作比较复杂,在能够进行最简单的读写操作之前必须要进行初始化和模式设置,是芯片工作在一个确定的工作模式。这些操作,包括读写操作,都是通过控制器传送命令来完成的。VDSD3G48AM有多个命令,这些命令定义如图3 VDSD3G48真值表所示:

图3 VDSD3G48真值表

VDSD3G48有多种功能,每种功能包括多个命令。本应用只涉及到最简单的单个读写操作,其余功能不讨论。VDSD3G48的操作流程包括:初始化和设置模式→读写操作→自动刷新。

1.3.1初始化和设置模式

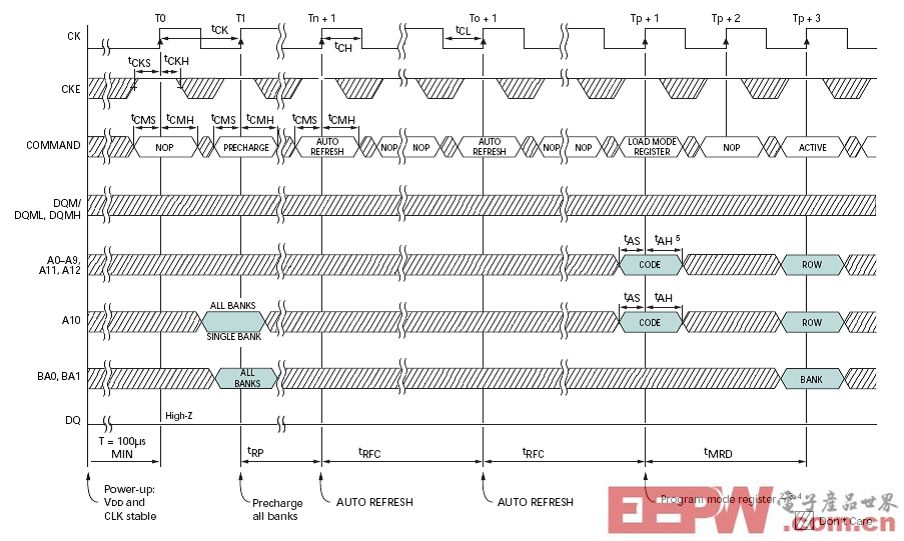

图4初始化和模式设置时序图

VDSD3G48功能比较多,时序比较复杂,所以上电后必须初始化,以指定一个确定的工作模式。当电源供给VCC和VCCQ后,需要100us的延时来确保时钟的稳定,而不是在这个期间发送NOP等命令,在这之后可以发送NOP命令。当满足了这个条件之后,至少要发送一个INHIBIT或NOP命令,接着发PRECHARGE命令,所有banks预充电,使VDSD3G48处于空闲状态。一旦在空闲状态,发出两个AUTO REFRESH命令。完成之后接着就是寄存器模式的设置。这一系列的操作如图4所示。

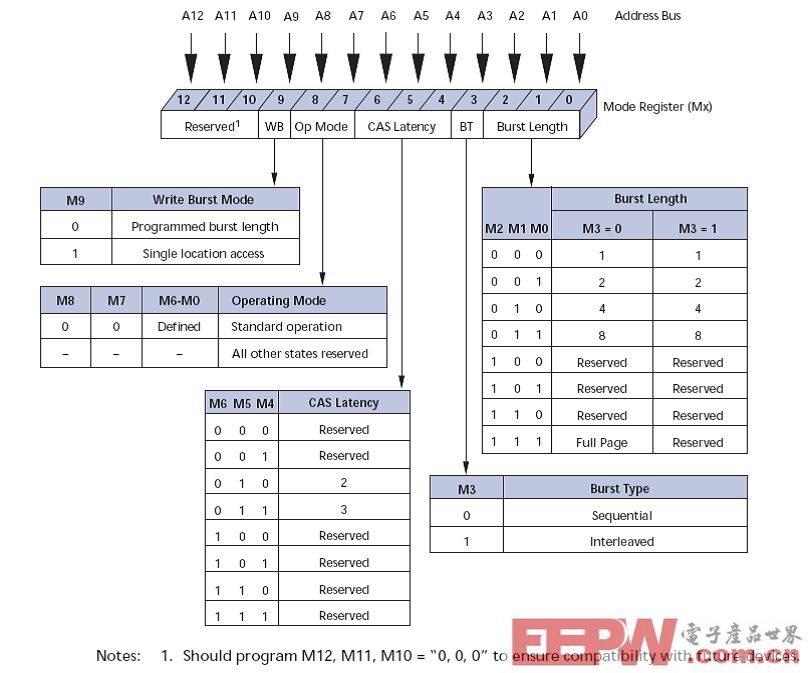

图5模式的定义

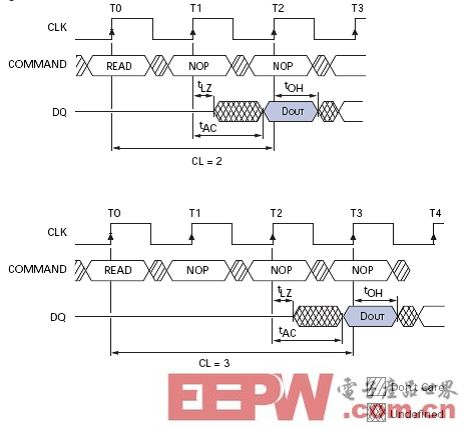

图6 CAS Latency时序图

上面涉及到的寄存器模式设置内容可从图5模式的定义中找到。模式的定义是通过地址线传送的,Burst Length定义爆发的长度,本应用案例只涉及单个读单个写,所以M2M1M0=000;BT定义连续还是交叉,选择连续BT=0,CAS Latency是在读周期读命令锁存以后到数据输出的延时时钟数,通常是2或者3,如图6 CAS Latency时序图所示。Op Mode中M8M7=00;WB=0,选择可编程爆发长度。

1.3.2自动刷新

VDSD3G48是一个SDRAM存储器,存储单元是一个电容,由于电容比较容易漏电,所以没隔一段时间必须给电容充电,以防数据丢失。目前公认的刷新周期为64ms,也就是说每隔64ms就要给每个单元刷新一次。对于不同容量的存储器,发出的刷新命令的间隔也是不同的,计算方法是:刷新间隔时间=64ms/行数。VDSD3G48有每片基片有8192行,刷新间隔时间T=64ms/8192=7.8125us,考虑到余量,取7us。

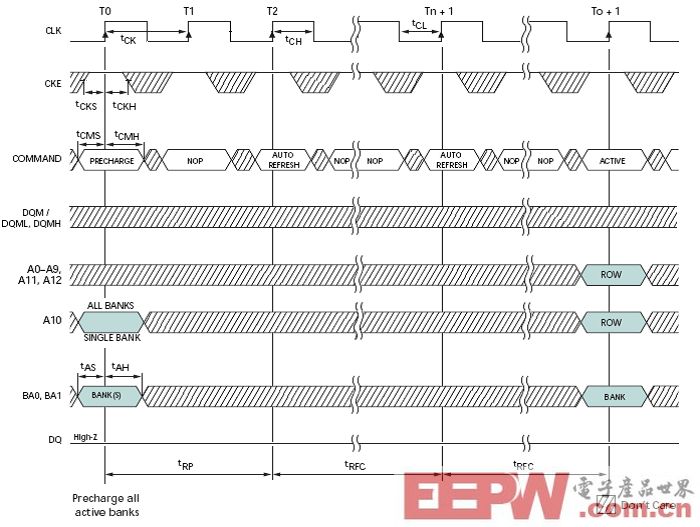

在发REFRESH命令之前,必须发PRECHARGE命令释放所有选中的banks。接着要等到TRP的延时之后才发REFRESH命令。所刷新单元地址由内部刷新控制器产生,所有REFRESH命令不用输入地址信号。所有操作如图7自动刷新时序图所示:

图7自动刷新时序图

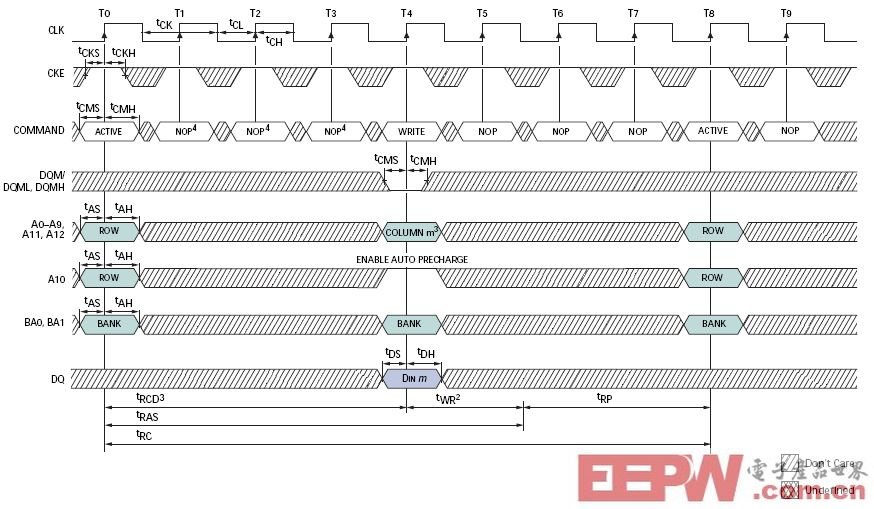

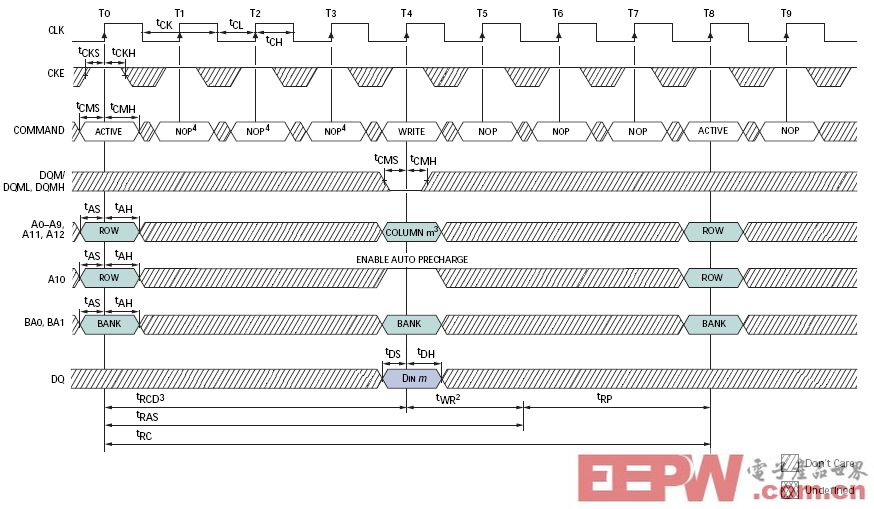

1.3.3单个自动预充电写

在写过程中,ACTIVE命令用于锁存来自A[12:0]的地址信号和来自BA1、BA0的bank信号,WRITE命令锁存来自A[9:0]地址信号,如果DQM为低,则来自DQ[47:0]上的数据则存入存储器阵列;如果DQM为低,来自DQ[47:0]上的数据将不忽略。A[10]用于选择是否自动预充电,如果选择,那么在写完成后选择的行将预充电。操作如图8单个写时序图所示:

图8单个写时序图

1.3.3单个自动预充电读

在读过程中,ACTIVE命令用于锁存来自A[12:0]的地址信号和来自BA1、BA0的bank信号,READ命令锁存来自A[9:0]地址信号。数据的输出将根据DQM信号的输入而定,在READ命令期间如果DQM为低,那么在经过两个时钟之后将输出数据(CAS Latency=2);如果DQM为高,那么将输出高阻态。A[10]用于选择是否自动预充电,如果选择,那么在读完成后选择的行将预充电。操作如图9单个读时序图所示:

图9单个读时序图

1.3.4 VDSD3G48控制器的实现

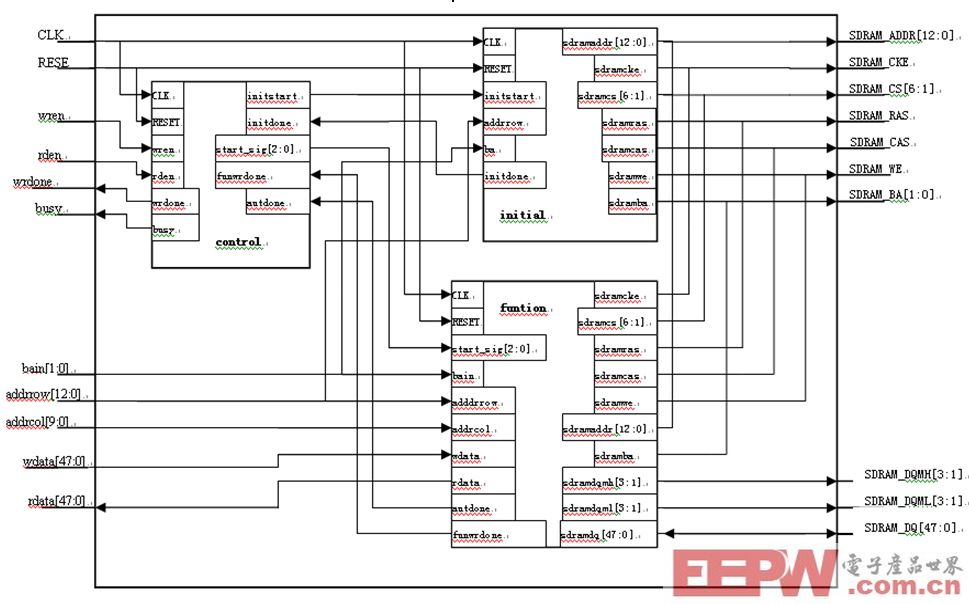

本案例的控制器只实现单读单写功能。即便如此,初始化模式设置和刷新功能是必不可少的。控制器原理框图如图10所示:

图10控制器原理框图

控制器分三部分:control逻辑控制、initial初始化和funtion功能部分。initial部分主要完成初始化模式设置;funtion部分主要完成刷新、读和写功能;control逻辑控制部分主要是控制协调initial初始化和funtion功能部分。

各个信号说明如表2所示:

表2 控制器信号说明

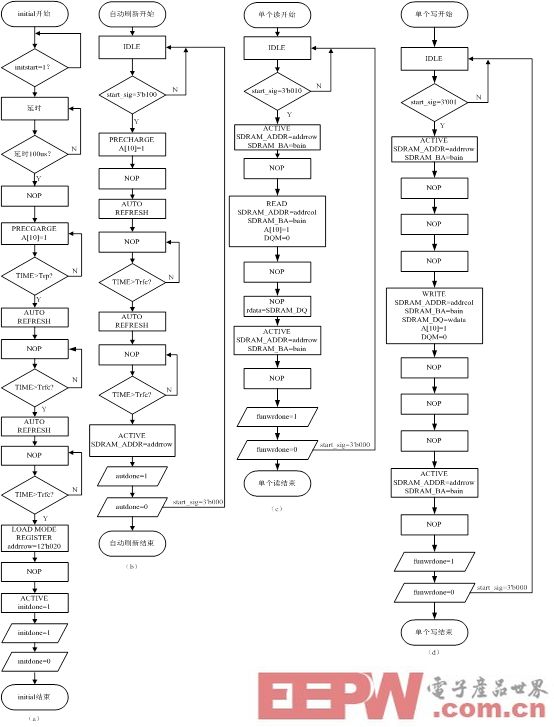

initial初始化

按照图4初始化和模式设置时序图,在初始化过程中,首先要延时100us,以便VCC和CLK稳定,接着发送NOP命令,再接着发PRECHARGE命令,此时发送A[10]=1,表示选择所有banks。延时tRP时间后发送AUTO REFRESH和NOP命令,如果延时大于tRFC,那么再发AUTO REFRESH和NOP命令。延时tRFC时间后发LOAD MODE REGISTER命令,地址信号送入设置的模式数据,之后发NOP命令,最好发ACTIVE命令,并送入行地址和bank信号。操作如图11(a)initial流程图所示:

图11(a)initial流程图 图11(b)自动刷新流程图

图11(c)单个读流程图 图11(d)单个写流程图

自动刷新

按照图7自动刷新时序图,FPGA实现自动刷新可按照图11(b)自动刷新流程图来实现,共有十个状态:IDLE、PRECHARGE、NOP、AUTO REFRESH、NOP、AUTO REFRESH、NOP、ACTIVE、autdone=1和autdone=0。这里并没有把NOP、AUTO REFRESH合并是因为不想增加难度。另外,ACTIVE和autdone=1也可以放在同一个状态中。自动刷新功能是由start_sig=3’b100发起的,之后就是按照十个状态按顺序进行。autdone=1和autdone=0两个状态在读时序中并没有出现,应用案例用着两个状态来产生一个正脉冲表示自动刷新动作完成了,用于各个部分协调。最后当start_sig=3’b000时返回IDLE状态这个动作很重要,因为自动刷新、读写操作都是用同一个状态变量,当刷新完成时状态变量处于autdone=0这个状态,假如刷新完成之后进行读操作,那么最终只进行了autdone=0这步操作,而不是从IDLE到autdone=0一系列的操作。其他操作原理同样如此

单个读操作

按照图9单个读时序图,FPGA实现读操作可按图11(c)单个读流程图来完成。实现共有十个状态:IDLE、ACTIVE、NOP、READ、NOP、NOP 、ACTIVE、NOP 、autdone=1和autdone=0。单个读功能由start_sig=3’b010发起的,之后就是按照十个状态按顺序进行。autdone=1和autdone=0两个状态产生一个正脉冲表示读动作完成了。最后当start_sig=3’b000时返回IDLE状态。

单个写操作

按照图8单个写时序图,FPGA实现写操作可按图11(d)单个写流程图来完成。实现共有十个状态:IDLE、ACTIVE、NOP、NOP、NOP、WRITE、NOP、NOP 、NOP 、ACTIVE、NOP 、autdone=1和autdone=0。单个写功能由start_sig=3’b001发起的,之后就是按照13个状态按顺序进行。autdone=1和autdone=0两个状态产生一个正脉冲表示写动作完成了。最后当start_sig=3’b000时返回IDLE状态。

逻辑控制部分

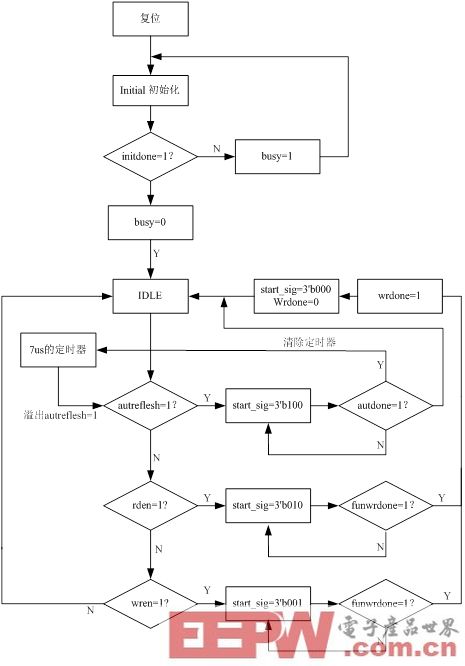

逻辑控制部分是一个重要的部分,是整个控制器的控制中心。逻辑控制部分主要功能如图12逻辑控制部分流程图所示。

逻辑控制部分在上电复位时,首先要完成初始化模式设置,当初始化模块完成初始化输出initdone时,逻辑控制部分输出busy=0,表示初始化完成了。接着进入空闲IDLE状态,在这个状态中进行刷新autreflesh、读rden和写wren的检测。当检测到autreflesh=1时,表示要进行刷新动作置start_sig=3’b100启动刷新功能,刷新完成之后得到反馈信号autdone=1,之后清除定时器,置start_sig=3’b100让功能模块状态变量回到空闲IDLE状态,并且回到逻辑控制部分的空闲状态。当检测到rden=1时,置start_sig=3’b010启动读功能,等到funwrdone=1读完成时,置start_sig=3’b000让功能模块状态变量回到空闲IDLE状态,并输出一个wrdone的正脉冲表示读功能完成,然后回到逻辑控制部分的空闲状态。当检测到wren=1时,置start_sig=3’b001启动写功能,等到funwrdone=1读完成时,置start_sig=3’b000让功能模块状态变量回到空闲IDLE状态,并输出一个wrdone的正脉冲表示写功能完成,然后回到逻辑控制部分的空闲状态。刷新读写功能的检测是有顺序的,也就是说是有优先级的,刷新比较重要,不立即数据就会丢失,所有首先检测刷新动作,相对来说读写并没有比较明显的区别,本案例读的优先级比写的优先级高。

图12 逻辑控制部分流程图

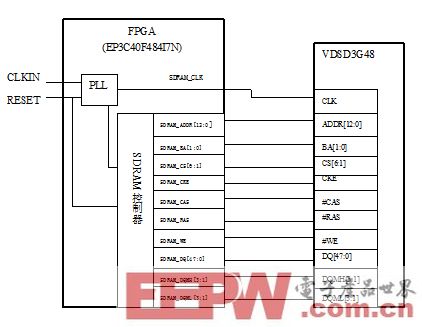

2、 FPGA与VDSD3G48的硬件连接

FPGA与VDSD3G48硬件连接图

如图所示,FPGA输入CLKIN时钟和RESET复位信号,其中复位信号能够复位锁相环PLL和SDRAM控制器,时钟输入经过PLL倍频之后一路送给SDRAM控制器,另一路送给输出送给VDSD3G48。FPGA的SDRAM_ADDR[12:0]、SDRAM_BA[1:0]、SDRAM_CS[6:1]、SDRAM_CKE、SDRAM_CAS、SDRAM_RAS、SDRAM_WE、SDRAM_DQ[47:0]、SDRAM_DQMH[3:0]、SDRAM_DQML[3:1]分别与VDSD3G48的ADDR[12:0]、BA[1:0]、CS[6:1]、CKE、#CAS、#RAS、#WE、DQ[47:0]、DQMH[3:1]和DQML[3:1]相连。

结 语

对于同步随机动态存取存储器(SDRAM)堆叠而成的立体封装的大容量存储芯片VDSD3G48,要进行初始化和刷新操作才能保证访问的正确性。同时基于SDRAM芯片立体封装存储器缩短了内部信号连接长度、减少了寄生效应,增强了抗干扰能力,可广泛用于车辆、卫星、飞机和空间站等领域。