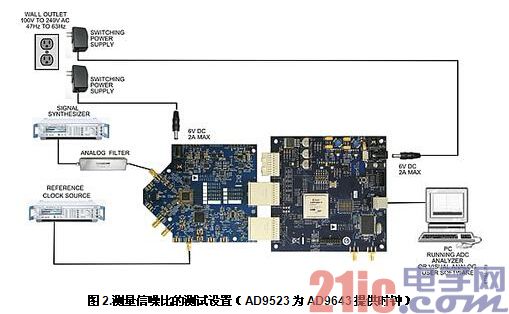

一些工程师一直在试图评估如何取得时钟源的相位噪声,并将其转化为最终达到ADC所产生信噪比的抖动。 现在来看一个电路示例,其采用AD9523低抖动时钟发生器来为14位、250 MSPS ADC AD9643提供时钟。 通过一些数学计算,我们根据AD9523的预期相位噪声性能以及AD9643数据手册规定的信噪比,能够确定预期信噪比值为68.763 dBFS。 回想一下,实际测量值是68.848 dBFS,如下图1所示。

借此能够计算出预估值,并且实验室测量结果与该计算值一致,总是令人欣慰的事。

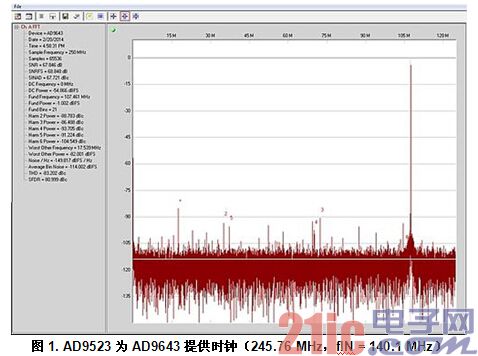

AD9643评估板,可以将其配置为采用AD9523来驱动AD9643时钟输入。 在此就不深入评估板配置的细节层面,而是更关注基础连接。如图2所示,利用AD9643评估板、HSC-ADC-EVALCZ数据采集板、壁式电源、Rohde-Schwarz SMA100信号发生器和PC。

AD9643评估板后,就可以如图中所示进行连接。 使用一个SMA100来驱动AD9643D的模拟输入,并用第二个SMA100来驱动AD9523的基准电压输入。 这些SMA100信号发生器为工程师提供了极低相位噪声的信号源,这对于器件获得良好的性能至关重要。 尽管如此,工程师还是想了解的是元件的性能,而非驱动元件的信号源。 这些信号发生器产生的相位噪声较低,对信号链的影响不大。

图中所示的PC需要安装ADI公司的SPIController和Visual Analog软件包。 SPIController软件提供了连接AD9643和AD9523器件SPI端口的接口,从而可以按工程师所想要的测试条件配置这些器件的相应设置。 Visual Analog软件控制数据采集板,并且处理来自ADC的数字数据,得到图1所示的FFT。其设置并不复杂,但是这值得探究,以深入理解如何得到之前所提出的数值的。