引言

在油田测井中,井下仪在井下采集大量信息,并传送给地面测井系统;但井下仪到地面这段信道的传输性能并不好,常用的NRZ码不适合在这样的信道里传输,而且NRZ码含有丰富的直流分量,容易引起滚筒的磁化,因而选用了另外一种编码——曼彻斯特码。曼彻斯特编码是串行数据传输的一种重要的编码方式。和最常用的NRZ码相比,曼彻斯特码具有很多优点。例如,消除了NRZ码的直流成分,具有时钟恢复和更好的抗干扰性能,这使它更适合于信道传输。

但曼彻斯特码的时序比较复杂,实现编解码器和单片机的接口需要添加大量的逻辑电路,给电路设计和调试带来很多困难。使用CPLD可大大简化这一过程。CPLD(ComplexProgrammableLogicDevices)具有用户可编程、时序可预测、速度高和容易使用等优点,这几年得到了飞速发展和广泛应用。上至高性能CPU,下至简单的74电路,都可以用CPLD来实现。而且CPLD的可编程性,使修改和产品升级变得十分方便。用户可以根

据原理图或硬件描述语言自由地设计一个数字系统,然后通过软件仿真,事先验证设计的正确性。PCB完成以后,还可以利用PLD的在线修改能力,随时修改设计而不必改动硬件电路,从而大大缩短了设计和调试时间,减少了PCB面积,提高了系统的可靠性。

1选用器件和开发软件

1.1选用器件

(1)XC95144

Xilinx公司的XC9500系列产品具有业界领先的速度,同时,具有增强引脚锁定结构和支持全面的IEEEStd.1149.1JTAG边界扫描,向用户提供了更高的灵活性。XC9500体系由多个同一功能块组成,每个功能块内含18个宏单元,引脚到引脚速度最快支持到5ns;支持125MHz时钟速率,I/O口接口电平5V、3.3V或两者皆可。其中XC95144内部有144个宏单元。

(2)HD-6408和HD-6409

HD-6408和HD-6409是Intersil公司的产品,两者均是曼彻斯特编解码器。

HD-6408编码器转换串行NRZ数据(通常来自移位寄存器)为曼彻斯特编码,增加一个同步头和一个奇偶位。解码器识别这个同步头,并判断出这是数据同步,还是命令同步,数据解码后移出NRZ码(通常送到移位寄存器中)。最后检查奇偶校验位。如果没有编码或奇偶校验方面的错误,解码器将输出一个有效信号,表明接收到一个有效的字。解码器能够向输入的曼彻斯特码字以很高的速率提供时钟恢复和优异的抗干扰能力。HD-6408使用在很多商业应用场合,例如安全系统、环境控制系统及串行数据链等。它的数据传输速率高达1Mb/s,开销很小,20位中有16位可用来传输数据。

HD-6409曼彻斯特编解码器使用原理与HD-6408略有差别,但基本相似。

1.2使用软件

CPLD编程软件选择XilinxFoundation3.1i。该软件界面友好,功能强大,提供了开发CPLD所需的整个流程,包括:编辑、综合、实现、仿真及下载等。该软件可人工指定引脚,编译各个子模块文件,并提供了两种仿真:功能仿真和时序仿真。其中时序仿真对时序提出了要求,是更严格的仿真。

2曼码控制系统设计

系统中,HD-6408以T2模式(20.8Kb/s)从地面接收数据,HD-6409以T5模式(93.75Kb/s)向地面发送数据。

接收时,HD-6408接收外部传来的曼码数据,转换成NRZ码在CPLD里进行串并转换,转换完成后产生接收中断,通知单片机取数据;发送时,单片机送给CPLD数据,进行并串转换,移位输出到HD-6409的输入端,由HD-6409编码发送出去。接收地址和发送地址均由CPLD解码产生。HD-6408和HD-6409所需的外部时钟源,通过CPLD对外部晶振分频得到。

2.2CPLD内部功能设计

2.2.1系统总体框图

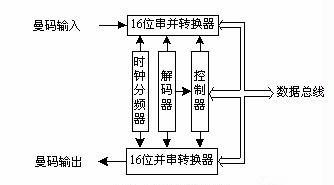

设计CPLD内部电路时,采用了模块化设计方法,内含5个模块:16位串并转换器、16位并串转换器、分频器、解码器及控制器。系统顶层逻辑框图如图1所示。

图1 系统顶层逻辑框图

以上模块均采用VHDL语言描述。控制器是核心部分,实现对HD-6408接收和HD-6409发送的时序控制。2.2.2 HD-6408解码时序

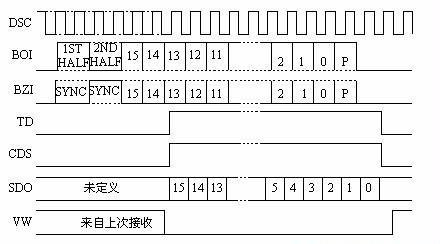

HD-6408的接收时序如图2所示。

图2 HD-6408的接收时序图

1)引脚定义

VW:输出字有效信号。DSC:解码移位时钟。TD:接收数据信号。SDO:串行数据输出。BZI、BOI:双极性数据输入。

(2)解码时序过程

解码器一直监视数据输入线,当接收到有效的同步头和两个有效的曼彻斯特码数据位后,便开始输出。当同步头被识别后,CDS引脚输出同步的类型:如果接收的是命令,便输出高并保持16个DSC周期;如果接收的是数据,就继续保持低电平。TD变高,并在SDO输出NRZ数据期间一直为高。SDO输出一个字后,开始检验奇偶位。如果曼彻斯特码和奇偶位都正确,VW信号输出高,此时解码器开始寻找新的同步头,开始下一个接收周期。接收到新的有效的同步头和两个曼彻斯特码位后,VW信号被复位;否则,在持续大约20个DSC周期后,VW信号变低。

2.2.3HD-6409发送时序

HD-6409发送时序如图3所示。

图3 HD-6409发送时序图

1)引脚定义

SD/CDS:串行NRZ码数据输入。CTS:清除准备发送信号。ECLK:编码时钟。BZO、BOO:曼彻斯特编码数据输出。

(2)编码时序过程

CTS信号高无效,低有效。在CTS信号的下降沿,引脚BZO和BOO开始发送同步序列(8个曼码“0”组成)。同步序列后就是命令同步脉冲(由1.5位高电平和1.5位低电平组成)。在输出命令同步脉冲时,NRZ数据在ECLK的下降沿通过SD/CDS引脚输入,这些数据编码后在命令同步序列后持续输出。这些码字没有奇偶校验和字结构。编码数据块的长度由CTS决定。

2.2.4VHDL源程序

控制器的VHDL源文件如下(程序较长,附核心部分):

process(controlcs)beginif(controlcsventandcontrolcs=1)thencontrol_data<=databus;endif;endprocess;

ee08<=resetandcontrol_data(0);lclk595<=nottd08;sclk595<=td08anddsc08;lclk597<=control_data(3)andqq_out;sclk597<=(not(esc08andsd08))and(noteclk09);tdd08<=not(td08);cdss08<=not(cds08);cts09<=control_data(1);load<=(ee_bitor(not(control_data(1))))andqq_out;dr08<=control_data(2);ss08<=control_data(4);mr08<=control_data(5);

信号说明如下:control_data——8位控制寄存器;controlcs——控制寄存器片选信号,低有效;mr08——hd-6408的主复位信号,高有效;dr08——hd-6408的编码器复位信号,高有效;ee08——hd-6408的使能信号,高有效;ss08——编码同步头选择;cts09——hd-6409的使能信号,低有效;lclk595——串并转换器的载入数据信号;sclk595——串并转换器的时钟信号;lclk597——并串转换器的载入数据信号;sclk597——并串转换器的时钟信号;load——16位计数器载入初值信号;qq_out——16位边界指示器;tdd08——触发中断信号。

3仿真与实现

本系统采用Xilinx公司生产的XC95144芯片,使用XilinxFoudation3.1i软件进行开发。所用VHDL程序通过时序仿真和下载后,观察波形并进行实际验证,可以正确地接收和发送曼彻斯特码,符合设计要求。

4结论

本系统时序配合严格,运行可靠,易于修改;可以根据需要,灵活地加入各种各样的使用曼彻斯特码通信的系统中。