近年来,随着集成芯片制造技术的发展,可编程逻辑器件(PLD)在速度和集成度两方面得到了飞速提高。由于它具有功耗低、体积小、集成度高、速度快、开发周期短、费用低、用户可定义功能及可重复编程和擦写等许多优点,应用领域不断扩大,越来越多的电子系统开始采用可编程逻辑器件来实现数字信号处理,从而使通用DSP芯片难于完成的一些时序组合逻辑和某些简单的大运算量的数学计算得以实现。继QuickLogic和XILINX分别开发了内含嵌入式FIR core的CPLD之后,ALTERA公司又推出了新一代可编程逻辑器件Stratix系列,其性能完全满足高速数字信号算是系统的设计要求。

1 Stratix系列器件的主要特性

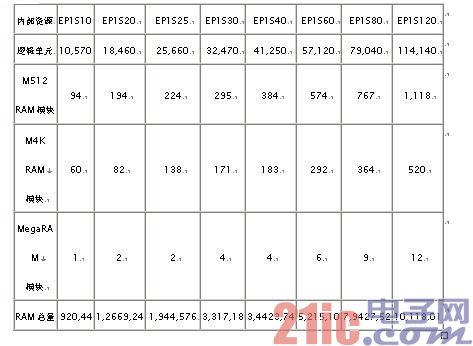

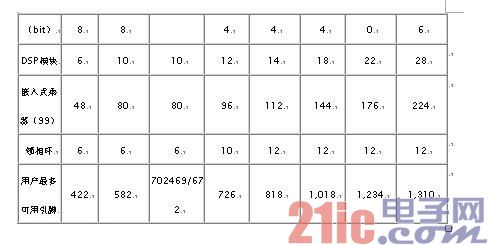

同其它含有嵌入式FIR core的CPLD相比较,Stratix系列CPLD采用了1.5V内核,0.13μm全铜工艺,由QuartusII 2.0以上版本软件支持,可以重复编程,通过JTAG接口或者EPROM加载程序,内部有DSP模块、PLL、大带宽高速I/O接口和大容量存储模块。主要内部资源参见表1。

表1 Stratix器件内部资源表

该系列CPLD主要特点包括:

• 高性能体系:Stratix系列器件的新结构采用了DitrectDriveTM技术和快速连续MultiTrackTM互联技术。 MultiTrackTM互联技术可以根据走线不同长度进行优化,改善内部模块之间的互联性能。Altera公司特有的DirectDriveTM技术保证片内所有的函数可以直接连接使用同一布线资源。这两种技术与QuartusII 2.0以上版本软件提供的LogicLock(tm)功能相结合,便于进行模块化设计,简化了系统集成。Stratix系统器件片内的全局和本地时钟资源提供了多达40个独立的系统时钟,有利于实现最丰富的系统性能;全新的布线结构,分为三种长度的行列布线,在保证延时可预测的同时,增加了布线的灵活性。

•大容量存储资源:Stratix器件中的TriMatrix存储结构具有高达10Mbit的RAM和高达12Tbps的峰值存储带;有三种不的嵌入存储模块类型,它们都具有混合宽度和混合时钟模式嵌入移位寄存器功能,可用于多种不同的场合:

512bit M512模块(512×1bit到32×18bit):512位模块加上校验,可用于接口速率适配的FIFO。

4Kbit M4K模块(4096×1bit到128×36bit):4K位模块加上校验,可用于小型数据块存储和多通道I/O协议。

512Kbit MegaRAM模块(64K×9bit到4K×144bit):512K位RAM加上校验,可用于存储大型数据块或者Nios TM嵌入式处理器软核代码等。

其中,4Kbit M4K模块和512Kbit MegaRAM模块支持完全的双端口模式。所有存储资源分布在整个器件中,设计者可根据设计的存储器类型和容量大小,通过Altera Quartus II软件的MegaFunction函数,灵活选择不同参数,配置成特定存储容量的RAM、DPRAM、FIFO等特殊模块。

•高带宽 DSP模块:Stratix DSP模块包括硬件乘法器、加法器、减法器、累加器和流水线寄存器。各个功能单元之间有专用的走线,具有针对Stratix器件内部大量存储器的专用存储器结构接口,因此通过优化设计,DSP模块可提供高达2.0GMACS的DSP性能,并且具有尽可能小的布线拥塞。

Altera Quartus II软件的MegaFunction提供了多种DSP模块操作模式。每一DSP模块可针对不同的应用,通过选择合适的DSP模块操作模式,实现8个9×9 位乘法器、4个18×18位乘法器或一个36×36位乘法器。当配置为36×36位乘法器模式时,DSP模式还可实现浮点算法。专用的乘法器电路支持带符号和不带符号乘法操作,并可在不带来任何精度损失的情况下,动态地在两种运算之间切换。

Stratix器件的DSP模块提供了高于DSP 处理器的数据处理能力,并且更为灵活和经济。每一Stratix DSP模块可提供多达8个运行在250MHz的并行乘法器,数据吞吐能力高达2GMACS。最大的Stratix器件EP1S125包括28个DSP模块,可完成高达224个并行乘法操作,并提供56GMACS的总线数据吞吐能力;而传统的DSP处理器最多仅可同时进行8个并行乘法操作,数据吞吐量也只有8.8GMACS。除了DSP模块中的专用乘法器以外,还可利用逻辑单元(LE)实现乘法器和DSP功能。例如,可在Stratix器件中利用大约 9600个逻辑单元实现一个256阶FIR滤波器。Stratix系列的EP1S120包括大约114140个逻辑单元,可以容纳11个这样的滤波器。每一滤波器可运行在200MHz,这意味着通过利用LE可提供563GMACS的器件总吞吐能力。结合DSP模块提供的56GMACS数据吞吐能力,Stratix器件可提供高达620GMACS的数据总吞吐能力。因此Stratix器件适用于大数据量数字信号处理。

•支持多种 I/O标准和高速接口:Stratix器件支持现有和将来的多种高速接口,如SFI-4、SPI-4、HyperTransport和RapidIO;多种高速外部存储器件接口,如DDR SDRAM/SDR SDRAM、ZBT、QDR、QDRII和DDR SRAM/DDR FCRAM;也支持多种单端和差分I/O标准,如LVDS、HyperTransport、LVPECL、PCML、SSTL和STL,能够在不同接口电平和协议下高速传送数据。典型的True-LVDSTM专用电路包括SERDES电路、差分I/O缓冲器、数据定位电路和精确调整时钟数据关系的锁相环(PLL),具有840Mbps性能,提供很高的数据吞吐能力,能够确保数据在所需的高比特率下可靠地传送和接收。

•时钟管理功能:每个 Stratix器件有多达12个PLL和40个全局,采用全功能的嵌入式锁相环(PLL)管理片内和片外时钟,可以进行频率合成、倍频、分频、调整相位和延迟。Stratix器件提供了两种PLL:增强型PLL支持外部时钟反馈、时钟转换、PLL重置、可编程带宽等功能;快速型PLL用于优化高速差分 I/O端口和全局时钟,实现最丰富的系统性能。

•终端技术:Stratix器件的片内终端技术提供了串行、并行、差分、单端片内端接电阻,实现了驱动阻抗匹配,减小了传输终端反射,改善了信号的完整性,提高了差分和单端I/O传输信号的质量和可靠性。同时,由于去除了多个分立终端电阻,减少了部件数量,从而减小了印刷电路板的复杂性,优化了印刷电路板的布局和布线。

•NiosTM软核嵌入处理器:NiosTM软件嵌入式处理器为Stratix、APEX等高端CPLD设计,可以实现SOPC(System-on-a-Progamable-Chip)集成。它提供了16 位专用指令集、ALU、同步地址发生器、16或32bit数据总线、各种外设(如定时器、SRAM、FLASH)和接口(如UART、PIO、SPI、 PWM、SDRAM接口和IDE硬盘控制器等),把微处理器的优点和PLD异常强大的DSP处理器功能结合在一起。DSP设计者采用Stratix DSP模块和Nios软核处理器,可以充分利用高性能DSP模块和软核处理器为软件算法实现所需的控制逻辑,通过硬件CPLD完成软件DSP算法。

•器件配置和远程系统升级:配置了差错恢复电路,确保了远程可靠、安全地系统升级和差错修复。如果恢复电路在重配置错误时,差错恢复电路将安全地回到初始的设置。

2 Stratix器件的典型应用

在高速信号处理系统中,通用DSP已经无法满足实时性、快速性的要求。设计者经常采用DSP+CPLD的结构,将任务分解成DSP完成的计算方式及控制结构比较复杂的信号处理算法和CPLD完成的时序组合逻辑及某些简单的运算,从而使系统处理能力显著提高。采用Stratix器件设计了高速数字信号预处理模块。

2.1 Stratix器件应用设计

高速数字信号预处理模块用于对原始数据进行滤波降采样处理,达到降低采样率、减少数据量、提高系统实时性的目的。具体结构如图2所示。原始数据通过FPDP端口接收并经过大容量DPRAM,并通过PCI总线送回主机,进行现场数据保存;另一方面抛弃辅助数据,提取真实数据包后,传送到降抽样滤波器,其结果由通用浮点DSP芯片ADSP21160读取,通过特有的Link Port传送到主处理板。所有FIFO、DPRAM、DSP模块均使用EP1S25内部资源。这种CPLD+DSP的混合结构设计可以同时具有DSP运算能力强和EP1S25速度高、资源丰富、设计灵活的特点,能适应大数据流的处理。

2.2 FIR滤波器仿真设计和参数计算

设计的核心部分是基于Stratix EP1S25设计的两个结构相同的低通滤波器,分别对I/Q两路原始数据进行滤波处理,使得其带宽降低。为了选取适当的滤波器阶数,必须在滤波效果和运算量之间进行折中。单纯从滤波效果的角度讲,滤波器阶数越高,越能逼近理想的矩形通带,提高抽样后信号的信噪比。但是阶数越高,运算量就越大,因此必须限制滤波器的阶数。综合考虑EP1S25中DSP模块数量与信号指标要求,即可确定滤波器的阶数。完成分析之后,在MATLAB下计算滤波器的参数,然后将参数归一化,重新分析滤波器性能是否满足要求。归一化后的参数可以直接作为FIR滤波器参数供CPLD设计使用。

2.3 基于CPLD的抽样FIR滤波器的结构设计

基于CPLD设计的FIR滤波器结构可以采用以下几种类型:直接型FIR滤波器、倒置型FIR滤波器和降抽样型FIR滤波器。直接型FIR滤波器是CPLD 实现FIR滤波器的最常用结构,来源于FIR公式的推导,是一种常见的模型。考虑到FIR的参数是对称的,可以采用对称的直接型结构。倒置型FIR滤波器是直接型FIR滤波器的变形,与直接型不同之处在于:直接型的加乘器是完全对称的,在设计中,可以统一的加法器、乘法器后插入缓存器,对计算结果进行暂存,实现对数据的流水处理;而倒置型不具备这个特点,它的乘加器运算必须在一个时钟周期内完成,否则运算错误。降抽样型FIR滤波器,在结构上类似于直接到FIR的并联,与前面两种滤波器的最大不同之处是边滤波边抽样。

前两种FIR滤波器通常用于串行输入数据的情况下。直接型由于对称结构,可以采用流水调度,所以工作频率很高,但是数据延迟比较大,40阶的滤波器可以达到20个时钟周期,控制比较复杂;倒置型结构的优点是没有数据延迟,控制简单,但是工作频率很低,与CPLD的乘加器性能有关;降抽样型FIR滤波器适用于输入数据是压缩数据的情况,即输入的数据由多个原始数据组成,可以避免数据拆包重组和滤波后的抽样,便于CPLD设计,最大的特点是可以在较低的时间频率下完成滤波抽样,不会造成数据的积累。从结构上分析,降抽样型 FIR滤波器和直接型类似,也存在控制复杂的问题。

2.4 降抽样型FIR滤波器的仿真结果

设计中通过调用Altera Quartus II软件的MegaFunction中的乘加器实现了一个32阶降抽样FIR滤波器。通过仿真,该滤波器完成对输入的4096点数据流的滤波和1/4降抽样的实时处理,只需要1024个时钟周期,输出延迟10个时钟周期,处理速度大大高于通用DSP,仿真的最高工作频率fmax达到了132MHz。在系统实际测试中,CPLD的最高工作频率fmax超80MHz,数据吞吐量达到2560Mbit/s。

采用Stratix系列的EP1S25 设计的高速数字信号预处理模块,在实验中,EP1S25承担了70%的运算量,使系统达到了实时数字信号处理的要求。实验同时证明,采用基于CPLD的 FIR滤波器和高性能DSP+CPLD的混合结构,可以同时具有DSP软件算法编程方便和CPLD结构灵活配置、适合固定算法的特点,对不同的算法都有较强的适应能力。