许多数字处理系统都会使用FPGA,原因是FPGA有大量的专用DSP以及block RAM资源,可以用于实现并行和流水线算法。因此,通常情况下,FPGA都要和高性能的ADC和DAC进行接口,比如e2v EV10AQ190低功耗四通道10-bit 1.25 GspsADC和EV12DS130A内建4/2:1 MUX的低功耗12-bit 3 GspsDAC。 通常情况下,这些转换器的采样率都达到了GHz的级别。对工程师团队来说,除了混合信号电路板布局之外,理解和使用这些高性能的设备也是一个挑战。

这些e2v数据转换器具有带宽宽、性能好的特点—数据手册上通常称为模拟全功率带宽—即使是在高奈奎斯特区。(这种能力是不多见的。)正是因为有着优异的转换性能,才可以使用直接上转换和下转换,这样可以减少部件数量、降低功耗以及节省成本。

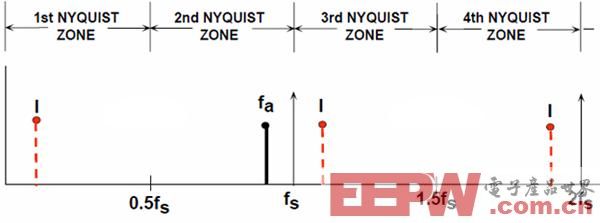

在高频时,奈奎斯特采样率(每个周期两次采样)是无法维持的。一个例子就是使用一个2.5GHz采样率的ADC去采样一个3GHz全功率带宽的模拟输入。根据奈奎斯特准则,高于1.25GHz的信号将会被混叠回第一奈奎斯特区,这些混叠图像是基础信号的谐波分量,因此和非混叠信号一样,包含了同样的信息。

相反的,如果你在使用DAC,进行直接转换时,你需要确定在上奈奎斯特区你想要使用的谐波。然而,对于DAC,在更高的频率下,你需要对DAC的衰减进行SINC补偿。因此,很常见的是通过仔细选择输入组件、阻抗平衡器、交流耦合电容以及通过设计前端模拟预滤波器等等去优化一个ADC或者DAC,使其能在一个奈奎斯特区中工作。

奈奎斯特区和混叠,1、3和4区中显示的是2区一个信号的镜像,基础信号(Fa)和谐波或者谐波含量的镜像

可以使用下面的算法来确定谐波或者谐波含量合成频率位置:

Fharm=N ×Ffund

IF (Fharm=Odd Nyquist Zone)

Floc=Fharm Mod Ffund

Else

Floc=Ffund-(Fharm Mod Ffund)

End

这里N是感兴趣的谐波的整数。

例如,采样率为2500MHz,基础频率是1807MHz,将会在第一奈奎斯特区有一个693MHz的谐波分量。

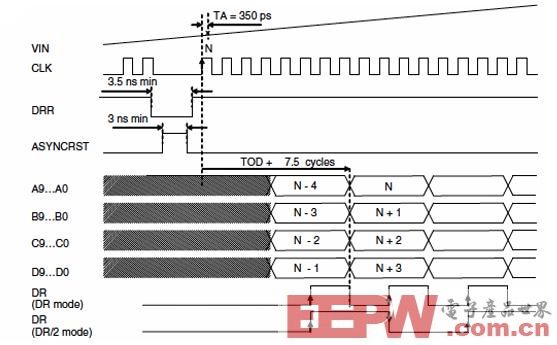

前面对频谱做了一些解释,另一个重要因素是这些设备和FPGA采用什么方式连接。许多高性能的数据转换器使用一个工作在较低数据速率的多路复用器来实现转换器的采样率-一般都是下图所示的使用FS/4或者FS/2,图中显示的是转换器的数据流在4条并行的10-bit总线(A, B, C, and D)上的分布:

转换器的数据流在4条并行的10-bit总线(A, B, C, and D)上的分布

通常情况下,这些数字接口采用的是并行LVDS总线,这样它们会占用许多的FPGAI/O管脚,但是,并行接口的延迟最小,并且由于它们使用差分信号传递方式,也可以降低辐射噪声,这在高性能系统中是非常重要的。

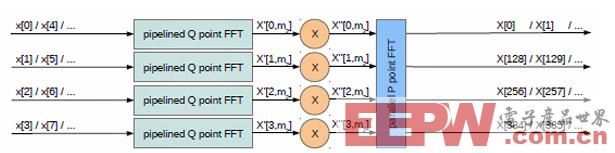

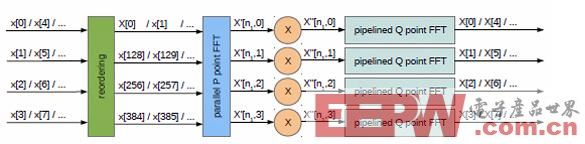

收到FPGA发出的4个数据流,你可能想知道在FPGA内部是如何处理数据的,在许多应用中,包括通信处理器和射电天文,都使用的一个常用的方法是使用组合或者分离的FFT结构,如下面两个图所示:

使用4个128点的FFT流水线,加上旋转因子和1个并行4点FFT,组合成512点的FFT

分离512点FFT,与组合FFT相反。与组合FFT不同的是,在前两个阶段,对高速输入有一个重组的操作

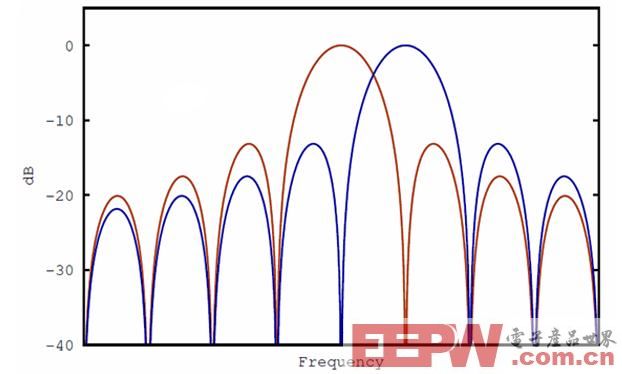

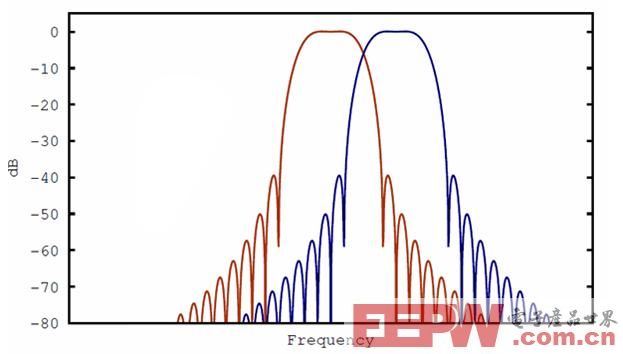

因为这些真实的数据样本,你将需要寻找一个优化的方法以便于在FFT结构中对这些数据进行处理,高效的、大FFT的实现是一个复杂的研究领域,但是在FFT之前,许多应用使用加权叠接相加(WOLA)结构来改善频谱泄漏。下面两个图显示了使用一个矩形窗口的普通FFT和使用WOLA的FFT的行为对比:

使用普通FFT矩形窗口的相邻信道

使用WOLA方法的相邻信道,显示了更少的频谱泄漏

然后,根据应用的需求,对这些合成的FFT数据进行后处理。