1.引言

DAB发射机是数字音频广播(DigitalAudio Broadcast,DAB)重要组成部分.

DAB技术是欧洲尤里卡项目之一,目前已经非常成熟.DAB采用先进的数字技术,正交分频复用技术(OFDM),能以极低的数据传输率及失真下传送CD质量之立体声节目,可解决传统模拟广播接收不良及干扰问题.DAB发射系统包括信源编码.信道编码.时间交织.频率交织.OFDM调制和射频部分.射频部分包括上变频和增益放大,用来把基带信号搬移到发射频率上并将其放大.

FPGA技术不断进步,成本和功耗不断下降的同时性能和容量在大幅上升,FPGA也代替MCU越来越多的嵌入到系统中去.

为了便于系统集成,本文设计FPGA系统嵌入到DAB发射系统中,使得开发变得方便灵活,同时也降低了成本.

2.FPGA的SOPC系统构成

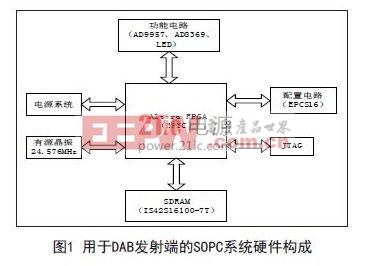

本文设计了用于DAB发射端的SOPC系统,该系统硬件框图如图1所示.系统中FPGA采用ALTERA公司的CycloneIII系列芯片EP3C16Q240C8N.FPGA中的NiosII软核处理器完成数据的控制和指令传送,还可以在FPGA上实现OFDM调制.配置芯片选用EPCS16,片外扩展存储器为IS42S16100-7T.框图中,功能电路是用来实现DAB发射功能的,它包括数字上变频(其中已经包括A/D和D/A转换).信号放大.USB传输等.

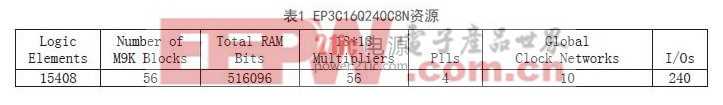

根据DAB发射系统设计可以得出系统中各个单元所需的资源:逻辑单元.寄存器.引脚.内存.乘法器单元.锁相环分别为8839.4719.104.202752bits.6和1.这款芯片为QPFP封装,芯片资源见表1.

2.1 配置电路

FPGA芯片按配置速度快慢依次为:

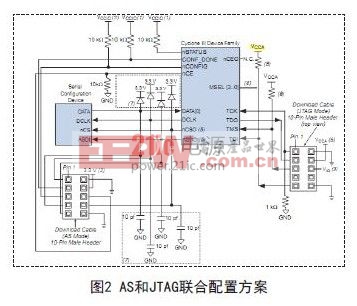

Active parallel(AP)模式.Fast passiveparallel(FPP)模式.Active serial(AS)模式.Passive serial(PS)模式.另外还有用于调试的Joint Test Action Group(JTAG)模式.本文FPGA同时配置AS模式和JTAG模式.

根据cycloneIII的数据手册,配置方案由MSEL引脚决定.当使用AS和JTAG两种方式时,MSEL[3:0]为“010”.如图2所示为ATERA给出的AS和JTAG配置电路.

AS模式是指FPGA的EPCS控制器发出读取数据的信号,从而把串行FLASH(EPCS系列芯片)的数据读入FPGA中,实现对FPGA的编程.配置数据通过FPGA的DATA0引脚送入,数据被同步在DCLK输入上,1个时钟周期传送1位数据.本文中选取的配置芯片EPCS16SI8,有16Mbits的存储空间,可以支持DCLK时钟工作在20MHz和40MHz.

JTAG接口是一个业界标准接口,主要用于芯片测试等功能.ALTERA的FPGA基本上都可以支持JTAG命令来配置FPGA的方式,而且JTAG配置方式比其他任何方式优先级都高.JTAG模式是将配置数据存储在SRAM,掉电后需重新下载.它与FPGA的接口有4个必需的信号TDI,TDO,TMS和TCK以及1个可选信号TRST构成.

2.2 外部存储器电路

SDRAM比FLASH速度快,比SRAM存储空间大,在FPGA系统中一般把SDRAM作为NIOS处理器的RAM和程序运行空间.本文中选择IS42S16100-7T这款SDRAM作为FPGA的外部存储器.IS42S16100-7T的信号电压为3.3V,有16Mbits的存储空间,最大速度可达到143MHz.在SOPC Builder里根据时序参数表设置SDRAM控制器.

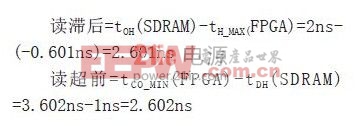

S D R A M的时钟应该和系统使用同一个PLL输出时钟,调试SDRAM和NIOSII的关键在于相位差,根据DAB发射系统,由F P G A的专用P L L时钟引脚输出系统时钟65.536MHz,相位差计算如下:

2.3 FPGA电源电路和时钟电路

稳定的工作电源是各个芯片和模块正常工作的前提,电源的稳定性也影响着器件的工作性能.FPGA芯片供电电压包括内核电压.I/O电压.PLL模拟电压.PLL数字电压和电压参考信号的参考电压.对于CycloneIII系列芯片来说,它的PLL模拟电压比CycloneII要高为2.5V.这些电压中数字电压与模拟电压要分开使用不同电源,并使用磁珠对其进行隔离.

为了滤除高频噪声,需要在芯片电源引脚与地之间加0.1f退耦电容.退耦电容在PCB板上要紧靠芯片电源引脚放置.

本文中的DAB发射板由AC/DC电源适配器提供电源,输入为100V-240V/50Hz-60Hz的交流电,输出为7.5V/3A的直流电.采用1117LDO稳压电源作为电源转换芯片,最大1A输出电流,固定输出1.2V.1.8V.2.5V.3.3V,为FPGA芯片以及系统中其他芯片提供电源.

文中采用24.576MHz的有源晶振作为系统的时钟,DAB发射电路的系统时钟为65.536MHz,由24.576MHz的经过SOPC系统中的PLL获得.此时钟也作为AD9957的标准时钟.

3.功能电路

3.1射频模块

射频模块完成数字上变频和信号增益放大.

数字上变频是指把数字基带信号搬移到射频中心频率,然后转换成模拟信号发射出去.本文中的数字上变频模块是AD9957是ADI公司推出的一款高性能的数字正交上变频器件,内置14bitDAC模块,内部系统时钟最高可达1GSPS,其功耗减小到50%以上.根据采样定理,一般要求DDS(数字频率合成器)产生的载波频率不能超过系统时钟频率的40%,所以其动态性能最高为400MHz,符合band3波段的要求.AD9957的外围电路包括18位并行数据接口和控制接口,其电源电压分3.3v和1.8v,两者都需要用数字电压与模拟电压分别供电.

信号放大部分采用可变增益放大器AD8369,其带宽范围600MHz,最大增益范围-5dB到40dB,通过芯片使能端DENB和增益选择控制端口BIT0~BIT3来控制信号放大.AD9957与AD8369之间使用阻抗为50ohm,用比率为4的射频变压器TC4-1WG2+进行阻抗匹配.

3.2 USB接口模块

USB接口模块主要是将在软件编码器上完成信道编码的数字信号高速的传输到FPGA进行IFFT运算.在设计中,USB接口模块的传输速度必须达到300Kbytes/s,才能满足实时传输数据的要求.本文中选用了由FTDI公司推出的FT245BL芯片.

该芯片性能优良,提供了一种在PC主机和外设之间进行数据传输的简单.低成本.高效率的传输方法.FT245BL需要6MHz晶振,通过芯片内部的振荡器和倍频产生12MHz和48MHz的时钟供芯片使用.

FT245BL需要提供5V和3.3V的工作电压.

4.结果

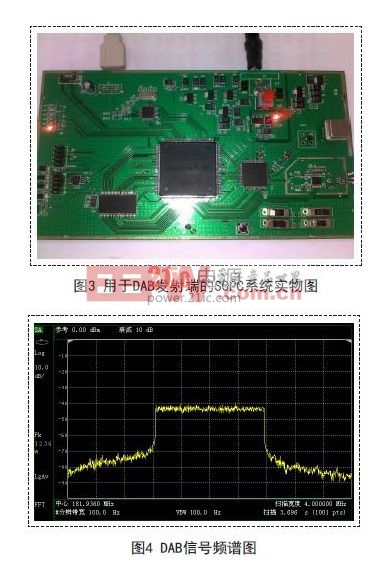

如图3所示为DAB发射端的SOPC系统硬件电路实物图,完成FPGA芯片配置和软件程序下载后,电路板上电,初始化成功后指示灯点亮.经过信道编码的DAB数据通过USB开始进入到硬件电路中进行调制.上变频和信号放大的处理,最后通过天线发射出去.如图4所示,为使用本文所设计的DAB发射机电路产生的DAB信号频谱,此DAB信号中心频率为181.936MHz,能被DAB接收终端接收,且播出的节目流利顺畅.

结果证明本文设计的这套电路板能运用FPGA的SPOC系统很好的完成DAB信号发射任务.