0 引言

软件无线电的基本思想是使用软件完成过去专用硬件才能完成的工作,其结构特点是让数字到模拟、模拟到数字的转换部分尽可能地靠近射频端,从而使信号尽早的数字化,用数字化器件来完成原来模拟器件才能完成的工作,这种思想是在数字通信发明之后电子领域的非常重要的技术革新。

软件无线电因其具有更低的设计成本、更大的使用灵活性和更高的性能,迅速在军事领域、公共安全领域和商用领域得到了很大的应用。软件无线电中的中频处理设计思路通常采用处理器加FPGA的方式实现,处理器实现系统控制和配置功能,FPGA实现信号的采集和实时处理功能。本文中频信号处理板采用双DSP加FPGA的方式实现。

1 硬件系统设计

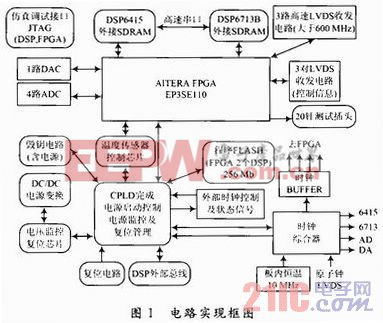

中频信号处理板设计采用以Altera公司的EP3S110和TI公司的TMS320C6415、TMS320C6713为核心,加以AD/DA、时钟电路等外围电路来实现中频信号的采样、调制解调、信息处理等功能。电路的实现框图如图1所示。

1.1 DSP部分

本设计采用两个DSP的方式,其中DSPTMS320C6713为浮点数字信号处理器,DSPTMS320C6415为定点数字信号处理器。TI的C67x和C64系列芯片都是非常成熟的DSP,其具有体积小、高速度、低功耗的特点,而且应用广泛,开发难度较低。器件容易获得。其中TMS320C6713是当前在军工领域广泛采用的浮点处理器,其最高支持300 MHz主频,工业级器件支持200 MHz,其内核采用超长指令字(VLIW)体系结构,有8个功能单元、64个32 b通用寄存器。一个时钟周期同时执行8条指令,运算能力最高可达到1600 MIPS/1200 FLOPS,支持双精度的数据类型。TMS32 0C6415最高支持1 GHz,能稳定工作在480 MHz,内核采用超长指令字(VLIW)体系结构,有8个功能单元、64个32 b通用寄存器。一个时钟周期同时执行8条指令,运算能力最高可达到4 800 MIPS。

在本设计中采用一颗TMS320C6713作为用户系统处理核心。DSP的外部存储器接口EMIF都需要挂接片外存储器。TMS320C6713有一组EMIF总线,位宽分别为32 b。TMS320C6415作为信号处理和控制处理核心。一颗TM$320C6415有两组EMIF总线,位宽分别为32 b。根据需要两个DSP挂接有如下片外存储器:

TMS320C6713需要挂接有如下片外存储器:

SDRAM:128 Mb/片,采用MT48LC4M32,EMIFA接口,32位同步存储器模式,100 MHz时钟速度。

TMS320C6415需要挂接有如下片外存储器:

FLASH:16 Mb/片,采用Am29DL160D,EMIF-B接口,8位异步存储器模式,90 ns操作速度。

SDRAM:256 Mb/片,采用EMIF-A接口,32位同步存储器模式,100 MHz时钟速度。

2颗DSP的EMIF总线除了和外部存储器连接外,还和FPGA的I/O相连,利用FPGA内部构建的双口RAM或者FIFO进行数据的传输。传输支持EDMA方式。为获得更好的数据吞吐速度,将外部存储器和FPGA构建存储器映射到不同的CE片选空间。

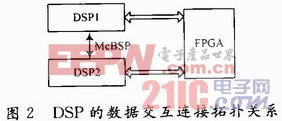

2颗DSP之间的数据通过FPGA进行交换,也可通过两个DSP之间的McBSP实现两颗DSP直接的数据交互,如图2所示。

在工程实现上,利用DSP内部的McBSP中断,可以让数据的交互在中断服务程序里面完成,使DSP的响应更为快捷。

1.2 FPGA部分

本设计中采用Altera公司的EP3S110作为实时信号处理核心。EP3S110是Altera公司具有全新架构的高密度产品。它采用65 nm工艺,与前期产品相比,器件的逻辑密度是前者的2倍,功耗降低了50%,性能提高了25%。本设计中采用的芯片,片上LVDS总线最高速率可以达到1.25 Gb/s,该芯片集成了106 500LE,896个18×18乘法器,16个全局时钟网络,88个等效LVDS通道,片上RAM为9 Mb的容量。该芯片在设计中主要完成的功能有中频信号的调制解调、编解码、频率点的置入、LVDS通路的建立、内部双口的构建等功能。

1.3 A/D,D/A部分

本设计中采用4通道高速A/D和1通道D/A,A/D采用14 b 105 MSPS的高动态、高精度、快速转换芯片,接收时4路A/D同时采集,满足对中频信号的采集要求,保证A/D的SNR在65 dB以上,D/A采用16 b 160 MSPS的高速数/模转换器,1路模拟输出,保证输出的杂散较低,频谱较纯。

采用的芯片为ADS6445和AD9957。ADS6445的主要特点为:

(1)高采样速率,采样速率高达125 MSPS。

(2)高分辨率(14位)。

(3)时钟输入可以使用LVCMOS,LVPECL,LVDS方式。

(4)ADS6445既有粗略增益调整也有精细增益调整。

AD9957的主要特点为:

(1)32位相位累加器。

(2)波特率高达25 Mb/s的SPI接口。

(3)内置1 024×32的RAM,可实现内部调制功能。

(4)内部采用1.8 V供电,超低功耗。

(5)内置的低噪声参考时钟倍频器允许使用低成本,低频率外部时钟作为系统时钟,同时可提供优良的动态性能。

(6)支持测试向量和幅度斜坡式控制功能。

1.4 CPLD和时钟部分

CPLD采用Altera公司的EPM2210F324来实现设计中的时钟综合器的配置和FPGA与DSP程序的加载等功能。整板正常上电后通过SPI配置时钟综合器,产生整板所需的时钟,配置完成后,CPLD控制FPGA采用FPP方式从FLASH中加载程序,当FPGA加载成功后,根据FPGA的配置引脚CONFI GDONE状态,将FLASH控制权交给DSP(6713),控制完成DSP(6713)的程序加载,然后控制DSP(6415)的程序加载。

时钟电路采用内部10 MHz恒温晶振和外部10 MHz原子钟的双时钟设计,两种时钟通过时钟综合器AD9522完成切换。双时钟的设计保证了整板的稳定性,正常工作时使用外时钟。当两个时钟有任一出现问题时,能快速切换到另一时钟继续稳定地工作。

2 软件系统实现

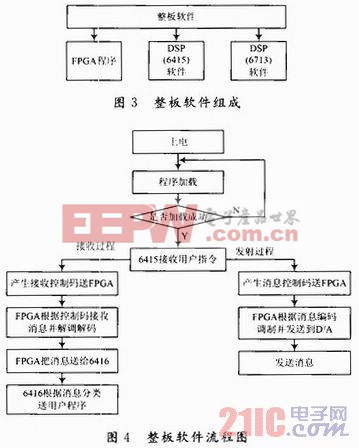

整板的软件由FPGA部分实现信号的调制解调、信号捕获、编解码等功能;DSP(6415)部分实现控制码的产生、系统的配置、通信的控制等功能;DSP(6713)部分用于用户程序的实现,可以根据用户的需要编写应用程序几个部分组成。整板软件组成图如图3所示,其软件流程图如图4所示。

3 试验验证

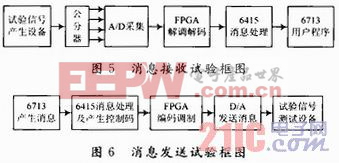

设计完成后进行了大量的试验,接收试验中试验设备产生一路70 MHz,带宽为5 MHz的MSK信号,通过一分四的公分器送给A/D,FPGA采样完成后进行解调和解码产生信息送DSP(6415),DSP(6415)根据消息进行处理后分类送DSP(6713),完成整板的接收试验,试验框图如图5所示。

发射试验通过DSP(6713)产生用户所需消息送DSP(6415),DSP(6415)根据用户送来的消息进行分类整理,生成发送消息所需的控制码,把经过处理的消息和控制码送给FPGA,FPGA根据消息和控制码进行消息的编码和调制送D/A发射。试验框图如图6所示。

通过大量的试验验证,充分验证了本设计的可行性和工程实现性。

4 结论

通过采用双DSP加FPGA构建的中频信号处理板方案能更好地完成中频的调制解调、编码解码和消息的预处理以及能开发用户程序。对时序要求严格的算法由FPGA实现,系统控制和消息处理由DSP(6415)实现,用户的应用程序由DSP(6713)来实现,这样使整个中频信号处理板调试更加方便,能更好地适应用户的需求。