最近有人在网上询问:“CPU每一代之间的差距体现在什么地方?”,以下选取一些芯片业从业者中经典而详尽的回答供读者研究。

一、破布(知乎用户):计算机体系结构,处理器微结构

我想您的问题可以分成两个部分:

每一代CPU的改进到底在什么地方?

CPU的设计是一个系统工程,通常可以分为微结构(学术界喜欢把micro-architecture翻译成“微结构”,传媒上多见“微架构”)、电路,器件,工艺这几大层面,每个层面内部都有很多细分方向,每个方向都有专家去研究,都有专门的工程团队在做。我现在接触比较多的是微结构这块,所以我只说微结构的改进。

微结构内部有很多地方是可以修改的,下面仅列举其中一部分:

(1)发射宽度(主要包括前端取指令的宽度、解码宽度、dispatch/issue宽度,retire宽度)。

(2)分支预测(包括但不限于预测器结构,预测准确率,branchresolve的延迟,流水线回退的耗时,以及寄存器重命名表能够保存多少个分支的快照)

(3)乱序执行窗口的大小(包括ROB,ReservationStation)

(4)Cache(扩充Cache大小,改进组织结构)

(5)Interconnect

(6)各种bypass,loopcache,etc.

每次Intel,AMD,IBM等巨头推出的新架构,您能在各大媒体上看到的新闻宣传,大多是从这些地方的参数入手,比如说Haswell把乱序执行窗口从168加大到192,诸如此类。

对于普通消费者而言,这些改进最终会贡献多大分量的性能差别?

上面列了这么多不明觉厉的术语,但是实际上,现在每一代新的CPU性能只能增长~10%左右。【出处为Hotchips2013DARPAMicrosystemsTechnologyOffice的DirectorRobertColwell所做的Keynote】

微结构研究的黄金年代我认为是在80年代~2005年前后,微结构上的很多经典成果,例如RISC,分支预测,超流水线这些东西,都是那时候火热起来的,当时的CPU性能提高比较快,这么多年过去,现在能挖的差不多都已经挖出来了,处理器的基本微结构已经相对固化,剩下的是一些小幅度的增量式改进,一点一点儿地抠性能。

现在业界的注意力已经转向其他方向,比如异构计算的概念最近就被炒的很热。

Bonus:CPU的性能瓶颈在什么地方?如何判断?

对于不同的程序,性能瓶颈也是不同的,比如说有的程序指令缓存miss率很高,流水线前端取不到指令导致停顿,有的程序是因为指令重命名时竞争寄存器的读取端口,有的程序是因为cache装不下工作集,所以很难一概而论。目前的大势主要是访存引发停顿。

通过CPU的参数判断CPU的性能瓶颈,我个人认为对于普通消费者而言是做不到的。那种一看网媒上公布的粗略架构图就嫩判断出CPU性能瓶颈的决不是仙人,而是异想天开的民科。那些巨头公司的架构师都是经过多年训练经验丰富,在大参数上犯下明显错误的可能性几乎为0,更不用说整个CPU是许多架构师的通力合作。

判断性能瓶颈需要做精确的量化分析,现在的CPU内部一般都集成了成百上千个性能计数器,有perf之类的专用工具可以读取这些地方的数值,统计各个不同部件的性能表现。这是一个比较专精化的领域,如果您想要了解这方面的知识,可以阅读《计算机体系结构:量化研究方法》作为起步。

二、吴恒:美国EE博士研究生在读,主攻化合物/锗半导体电子器件

看到大家基本都是从架构系统级的角度去思考这个问题,我就从物理层给一个答案吧.

CPU是由无数晶体管组成的,架构系统级管的是如何让这无数MOSFET(金属氧化物半导体场效应晶体管)合理并且高效的运行,物理层管的则是如何让单个MOSFET运行的更快.

关于工艺上的革新简直数不胜数,十年前我们使用的CPU(以pentium4为例)的特征尺寸(criticallength,也就是常说的线宽)为90nm,晶体管是平面MOSFET(planar-MOSFET),现在我们用的Core4XXX系列的特征尺寸是22nm,晶体管用的是3D鳍式MOSFET(FinFET).更小的特征尺寸意味着更大的驱动电流,更大的驱动电流意味着更快的响应速度,于是CPU的速度更快.

在这十多年中,CPU经历了:

1.单核CPU到多核CPU的改变,不再用简单的主频来拼性能(主频越高,功耗越大,散热问题越严重).

2.栅极氧化物:低K值二氧化硅(SiO2)到高k值二氧化铪(HfO2),用来解决随特征尺寸减小带来的栅极控制能力减弱的问题.

3.栅极氧化物兼容性要求:多晶硅栅极到金属栅极(n型和p型不同金属).

4.传统硅衬底到应变硅技术(strainsilicon,应变条件下Si半导体的载流子迁移率会得到非常大的提升,从而提高晶体管驱动电流).

5.SiGe源漏级技术(用来降低晶体管接触电阻,增大电流).

6.特征尺寸的不断缩小90-65-45-32-22nm,下一个目标就是今年的14nm.(特征尺寸的缩小能带来更大的驱动电流以及更高的晶体管集成度,进一步增强CPU芯片的运算速度和能力,同时也会带来更多的散热和功耗问题)

7.3D晶体管技术(用来增强在短沟道条件下的栅极控制能力).

8.SOI技术,绝缘体上硅技术,由IBM提出,是IntelFinFET阵营以外的另一大技术阵营.

Moore定律驱动着半导体产业的不断向前发展,其实在你不经意之间,无数人的奋斗成果和新技术,以及数以亿计的晶体管都被注入了那小小的1cm见方的硅片之中,这本身不就是一个很奇妙的事情吗?

从另一个角度上说,其实我们在不经意间参与了这人类历史上最伟大和最先进技术的变革之中了.

最后送几张图

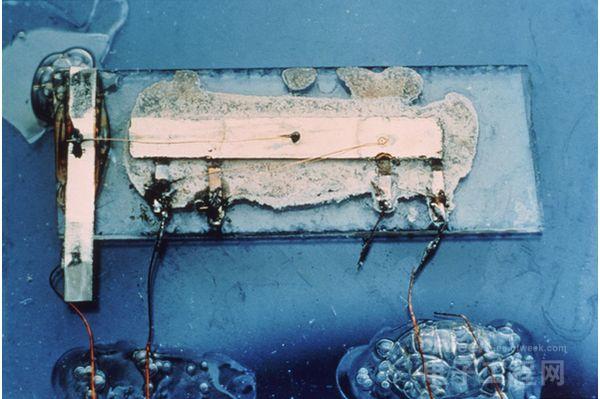

世界第一个集成电路(By Ti).

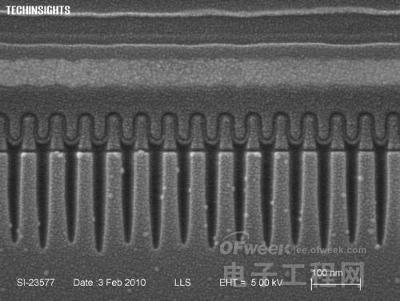

苹果A7芯片的截面图,图中每一个针状的结构都对应一个晶体管 (By Samsung).

3D 晶体管截面图, 注意比例尺. (By Intel)

一个完整CPU的截面图,上层是金属互连线,最下面的是晶体管.