摘要:文章主要阐述以单片机+CPLD的方案进行的LED大屏幕显示控制系统的设计。以单片机作为系统的数据通信控制和扩展其它功能,CPLD作为显示屏正常动态显示的硬件控制,采用模块化的设计,使结构简单,修改功能方便,同时充分利用了单片机实现多任务的特点,便于功能扩展,硬件电路简单。

LED大屏幕显示屏以亮度高、工作电压低、功耗小、小型化、寿命长、耐冲击和性能稳定、组态灵活等优点迅速成长为平板显示的主流产品,在信息显示领域得到了广泛的应用。

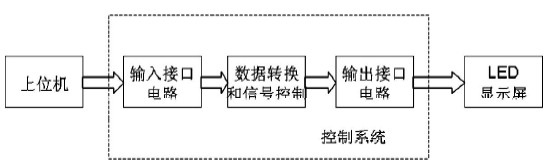

LED大屏幕显示屏主要由点阵或象素阵列、控制系统和传输接口以及相应的应用软件四部分构成。如图1所示控制系统负责接收、转换和处理各种外部信号以一定的规律和方式将信号传送到显示屏上显示。作为显示屏的核心部分,控制系统直接决定了显示屏的显示效果,也决定了显示屏性能的优劣(见图1)。

图1 控制系统框图

1 控制系统的硬件设计

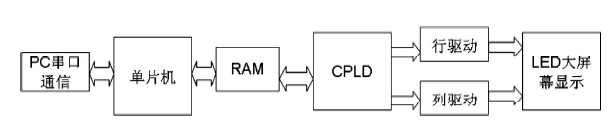

控制系统的实现方案很多,本设计采用单片机+CPLD的方案进行设计(如图2)。

图2 控制系统的硬件框图

单片机主要实现通信控制,既可以将存储器中的数据读取出来送往PC机,也可以将PC机编辑好的信息经过处理后存于存储器中,以方便控制系统的下一步处理。屏幕扫描逻辑采用CPLD为核心,CPLD的功能是从存储器中读取数据,将数据输送到屏体上,同时产生控制信号(见图2)。

1 . 1 主控单片机电路

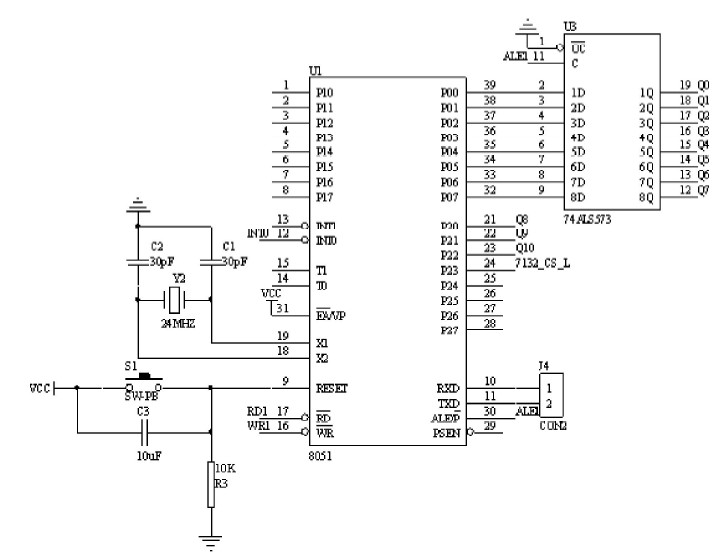

主CPU采用AT89C51单片机,外扩一片74LS573实现数据和地址总线的分离,用以与RAM进行信息通讯,串口与PC上位机连接。单片机电路主要负责整个系统的初始化、显示方式的处理、以及与PC机的通信等工作。主单片机电路原理图如图3。

图3 单片机原理电路

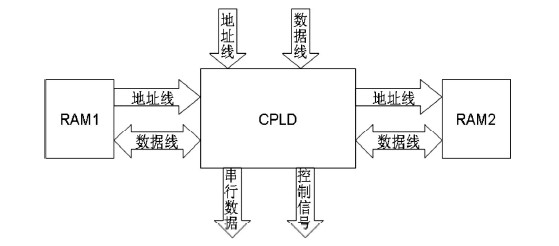

1.2 复杂可编程逻辑器件CPLD

CPLD复杂可编程逻辑器件是一种具有丰富的可编程引脚的可编程逻辑器件,不仅可实现常规的逻辑器件功能,还可以实现复杂而独特的时序逻辑功能。而且具有在系统可编程功能,便于进行系统设计和现场对系统进行修改、调试、升级。本设计中CPLD就是用来实现控制系统中的时序产生部分,并且协助对两片辅助RAM进行读写。结构示意图如图4所示。

图4 CPLD 的通信示意图

2 屏幕扫描逻辑的设计

2.1 屏幕扫描逻辑的设计思路

LED显示屏驱动电路主要采用动态扫描显示,动态扫描显示是在一个比较短的时间周期内将LED显示屏上需要发光的像素逐行分别点亮。动态扫描显示方式采用多行(16行即1/16扫描方式)的同名列共用一套列驱动器。

行扫描电路由译码器构成,逐行扫描信号。从第一行开始,按顺序依次对各行进行扫描。一旦该行选通,这一行上的相应像素就可以由列驱动信号点亮。当一行的扫描持续时间结束后,下一行以同样的方法进行显示。在1/16扫描方式中,就是把16行都扫过一遍之后,又从第一行开始下一个周期的扫描。

屏幕刷新频率关系到屏幕显示效果的好坏,从数据更新的角度来讲,扫描时钟频率越高,留给数据更新的时间就越少,不利于系统刷新;扫描时钟频率越低,扫描时间越长,将引起屏幕闪烁。一般来讲,这个刷新频率不能低于50HZ(帧频),否则,会产生屏幕闪烁现象。

2.2 主控电路的程序流程

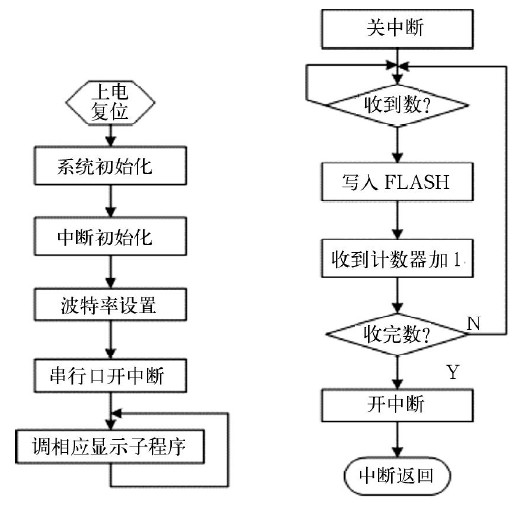

主单片机的主要功能是接受上位机下载的显示数据,向屏体提供显示数据和各种控制信号,软件由主程序和中断服务程序两部分组成,主程序负责进行显示,按要求读出显示数据并产生需要的控制信号;中断服务程序解决与上位机进行通信的问题(见图5、6)。

图5 主单片机控制程序图

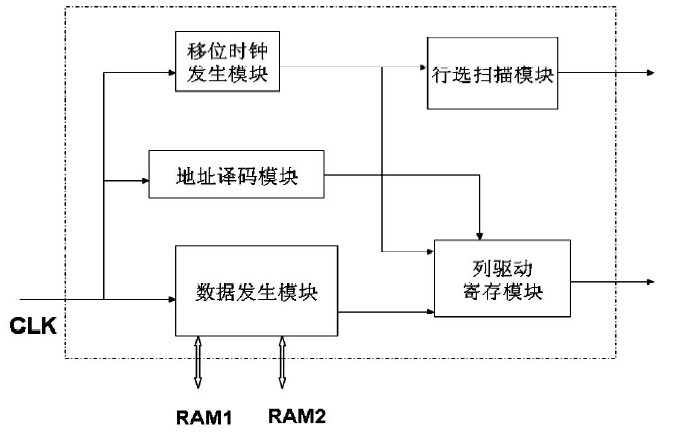

2.3 CPLD的程序设计框图

对CPLD的程序编写采用模块化编程方式。整个程序由数据发生模块、地址译码模块、移位时钟发生模块、行选扫描模块、列驱动寄存模块等组成。程序结构如图6所示。

图6 CPLD 的模块化设计框图

3 结语

本设计采用以单片机89C51为基础,结合CPLD简化了系统结构,减小了控制板面积,降低了系统的功耗和干扰,提高了系统的稳定性,并具有分布灵活、扩展方便等优点,使调试和维修变得更加方便。CPLD具有在线可编程的功能,通过软件对CPLD重新配置,可以实现对不同规格的控制,使系统具有通用性和扩展性。

参考文献:

[1].CPLDdatasheethttp://www.dzsc.com/datasheet/CPLD_1136600.html.

[2].AT89C51datasheethttp://www.dzsc.com/datasheet/AT89C51_810155.html.

[3].74LS573datasheethttp://www.dzsc.com/datasheet/74LS573_590916.html.

[4].1/16datasheethttp://www.dzsc.com/datasheet/1%2f16_2510134.html.