问题和测试

在某产品中,一颗CMOS sensor的复位信号CMOS_RST和休眠信号CMOS_STB分别使用了1.5K电阻上拉,并且也分别连接到了CPU(TI的DM355)的两个GPIO上。

由于发现了sensor的CMOS_RST和CMOS_STB信号一直处于不可控状态(经软件检测确认是管脚分配错误),仅靠1.5K上拉电阻使其维持在大约2.8V的高电平状态(貌似不太影响整个sensor的一般工作,正常高电平应该是3.3V)。因为产品有一些问题存在,在查错过程中找到了这两个异常GPIO,后文是对其的一些测试和研究。

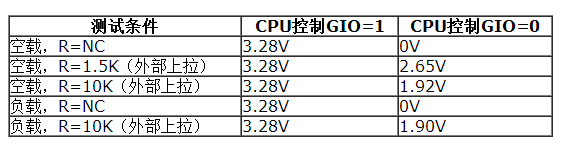

在CMOS_RST和CMOS_STB信号的1.5K上拉电阻不变的情况下,做了一些测试,发现CPU控制的GIO=0无法将实际的输出拉到低电平。对CMOS_RST信号做了一些测试,如表1所示。

表1

从表1的测试中发现,无论是上拉1.5K还是10K都无法在GIO输出低电平时使CMOS_RST的实际电压达到0.8V以下。

原因分析

查看CPU的datasheet,如图1所示。用于连接CMOS_RST和CMOS_STB信号的GIO100和GIO83内部有下拉电阻的设置,因此前面测试到外接1.5K或10K上拉电阻的低电平无法拉“低”的现象就可以解释了。

图1

此外,在DM355的datasheet并没有找到任何更多的信息,因此在TI官网一阵还找,终于发现了一些相关线索。在TI另一颗CPU中有关于GIO内部上下拉的比较详细的资料。

http://www.ti.com.cn/cn/lit/ds/sprs660e/sprs660e.pdf

page66

这里不仅比较详细的说明了TI的CPU内部会有PD/PU,也提到了设计者如何考虑外部PD/PU的使用,主要是一些如配置管脚或特殊应用的管脚,需要有一个较明确的状态。而对于内部的PD/PU,虽然也没有太明确的说明,但特权同学找到了相关配置PD/PU的选择寄存器,如图2所示是可配置的。不过,对于这个案例中使用的DM355,找遍了寄存器手册,还是没有任何“可编程”或PU/PD可设置的相关寄存器。因此,只能怪咱运气不好,惹不起咋还躲不起吗,解决办法有一个,so easy——

图2

解决策略

将连接到有PD的两个GIO信号外部的上拉电阻删除,问题解决。一个很细节的设计case,但它却是很可能启发一些大问题,所以望大家引以为戒。