高速高精度钟控比较器的设计.pdf

时间:01-16 09:32

查看:2531次

下载:162次

简介:

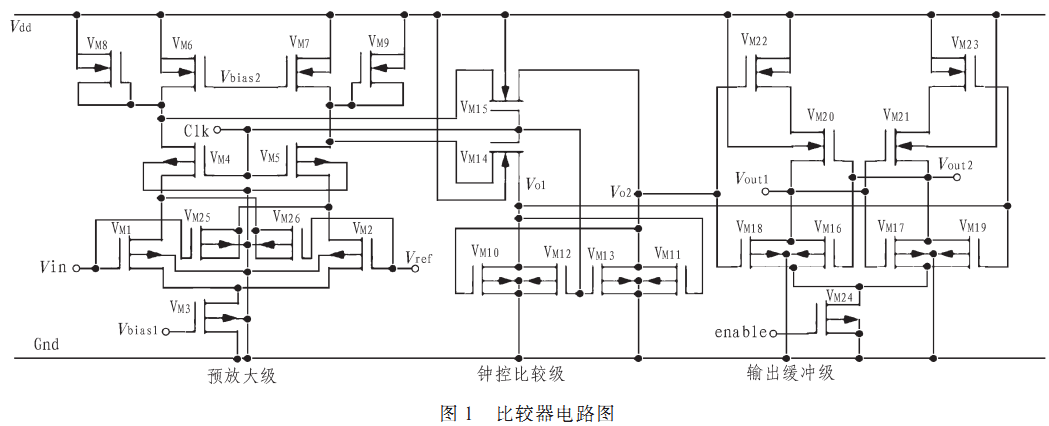

为满足10位高分辨率A/D转换器的需要,设计了一种高速高精度钟控电压比较器,着重对其速度和回馈噪声进行了分析与优化。该比较器采用前置预放大器结构实现了高比较精度,利用两级正反馈环路结构的比较锁存器提高了比较器的速度,隔离技术和互补技术的应用实现了低回馈噪声。基于TSMC 0.18 μm CMOS标准工艺,用Cadence Spectre 模拟器进行仿真验证,结果表明比较器的工作频率可达300 MHz,LSB(Least Significant Bit)为±1 mV,传输延时为360 ps,功耗为2.6 mW,可达到10位的比较精度。该电路可适用于高速高精度模数转换器与模拟IP核的设计。