TCLGU21机芯高清彩电属于数字窗系列,是在NU21机芯基础上派生出来的,主板电路完全一样,仅数字板。f二的倍行处理部分不一样,NU21机芯倍行芯片采用PW1235A,该机芯采用FLI2300,不仅电路结构简单,而且新增了许多功能。GU21机芯的代表机型是H1D34158H。

FLI2300是微科公司生产的最新总线控制型数字解码及的数字变频主芯片,其PAL制图像具有以下几种成像模式:100Hz逐点清晰、60Hz数字逐点、75Hz数字逐点、1520线数字增密;NTSC制图像具有60Hz数字逐点成像功能。

一、数字板简介

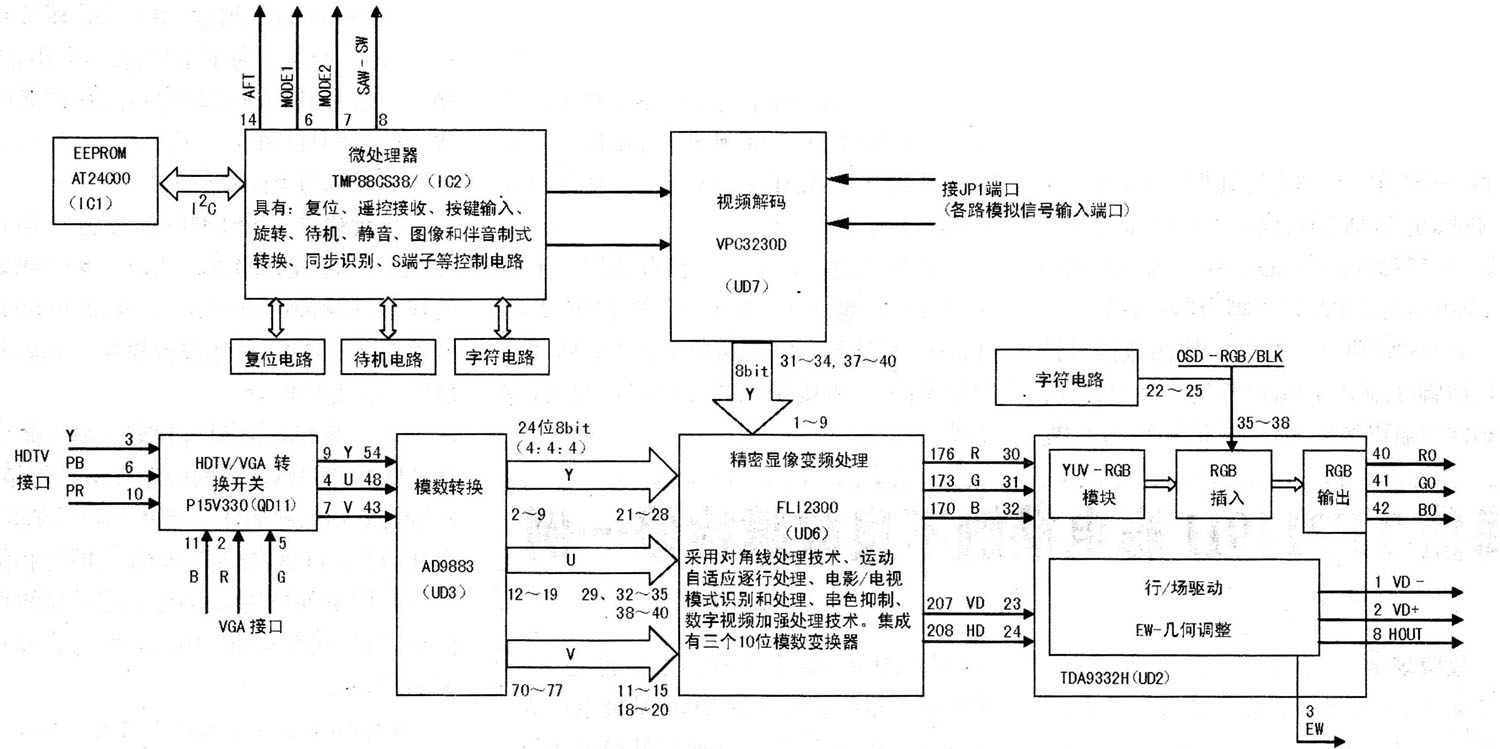

GU21机芯数字板电路主要由CPUTMP88CS38N(IC2)、24C00(IC1)、P15V330(QD11)、AD9883(UD3)、VPC3230D(UD7)、FLI2300(UD6):KM432S2030(UDl)、TDA9332H(UD2)等集成电路及一些外围元件组成,其组成框图见图1。

图1 组成框图

GU21机芯数字板通过JP1~JP5五个插座与外部电路连接。其中,JP1为从主板送过来的隔行模拟视频信号及ABL、FBP、VD+、VD-、VFB、EW、EHT、12V、5.2V电源等信号,输入的模拟信号进入VPC3230进行视频解码;IP2为遥控信号、按键信号、总线数据,与主板S001A的端口相连接;JP3为RGB,及消隐信号输出到CRT板;IP4为HDTV的信号输入端口;JP5为VGA的RGB及HS、VS同步信号输入端口。

所有的隔行视频信号都输入到视频解码器VPC3230D内部。VPC3230D是微科公司生产的梳状滤波视频处理器,该芯片集成了视频切换、Y/C分离(4H自适应梳状滤波器)、A/D转换、数字解码、pIp等功能。视频解码输出支持ITU-R601/656数字输出接口。

二、数字板信号流程分析

1.TV及隔行视频输入信号

一体化高频头输出的TV视频信号经电容CD131、RD130平滑滤波后,从VPC3230D(75)脚输入;S端子的C、Y信号分别经电容CD135,CD136耦合后从(71)、(72)脚输入;AV2的视频信号经电容CD129耦合后,从(73)脚输入;Cb、Y、Cr信号分别经LD21、CD139、CD123、RD111,CD128、LD28、CD138、CD132、RD21、LD22、CD141、CD140、RD122、CD130组成的滤波电路滤波后,从①~③脚输入。输入的视频信号经VPC323()D视频解码处理后,输出数字信号。

VPC3230D是一块总线控制型PAL/NTSC/SECAM制彩色电视信号处理集成电路,具有功能多、外围电路简单、性能优良等特点。VPC3230D(13)、(14)脚为总线控制端(SCL、SDA),与外围集成电路相连接;(15)脚外接的RD83、QD8、RDl04、DD6是一个复位控制电路,用于对芯片复位;(63)、(62)脚外接晶振XD1(20.25MHz),产生基准彩色所需信号。VPC3230D采用3.3V和5V供电。

VPC3230D(70)脚输出视频信号,经QD10、RD146组成的射随电路放大后,从QD10的发射极输出。VPC3230D(30)~(34)、(37)~(40)输出8bit的YC信号(简称8bit位格式的数字信号),送往FLI2300进行精密显像处理。

2.VGA及HDTV信号

VGA的RGB及Hs、Vs信号从端口JP5输入,VGA的RGB信号先由FB5~FB7、CD154、CD158、CD162滤波,再由QD4~QD6射随放大,最后送到P15V330(QD11)的②、⑤、(11)脚。

HDTV信号由端口JP4输入,HDTV的Y、Pb、Pr信号先由FB2~FB4滤波,再送入QD11的③、⑥、⑩脚。

P15V330是一个4通道2选1高性能视频模拟开关,具有导通电阻低、频带宽、低串扰等特点。VGA和HDTV信号经QD11切换后,从QD11的④、⑦、⑨脚输出RGB信号,经RD34、CD28、RD36、CD35、RD33、CD28电容耦合后,送到AD9883(uD3)(54)、(48)、(43)脚。

AD9883是ADI公司专为平板显示模拟前端接口设计的模数转换集成电路,采用80脚封装,3.3V供电电压。该IC内置三通道8位110MHz采样频率的AD转换器、同步处理器及时钟发生器、I2C主机接口等功能模块,其数字视频输出接口支持4:4:4的YUV信号输出。输入的YUV信号经AD9883处理后,从②~⑨脚、(12)~(19)脚、(70)~(77)脚输出8bit的数字YUV信号,分别送到FLI2300的(21)~(28)脚,(29)脚、(32)~(35)脚、(38)~(40)脚,(18)~(20)脚、(11)~(15)脚进行处理。AD9883的(30)、(31)脚是VGA的行同步和场同步信号输入端,(56)、(57)脚分别是SDA、SCL脚。AD9883的供电电压为3.3V,供电脚为(33)~(35)脚。

AD9883(67)脚(DATACK)输出数据时钟信号,(66)脚(HSOUT)输出行同步信号,(64)脚(VSOUT)输出场同步信号,(65)脚输出G复合同步信号,分别送到FLI2300④脚(IN-CLKl-PORTl)、①脚(HSYNCl-PORT1)和②脚(VSYNC-PORTI)。另外,AD9883(65)、(64)脚还分别与CPU(36)、(13)脚相连。

3.变频处理

FLI2300是Genesis公司推出的高质量数字视频格式变换器,采于CRT-TV的高整合数字视频转换的专利应用软件,可进行非线性和任意图形缩放比例、帧频比例转换,其应用框图如图2所示。

图2 应用框图

FLI230()①、②脚为TV信号的Hs和Vs同步信号输入端,(191)、(192)脚外接13.5MHz晶体振荡器(XD3),(45)、(46)脚(SCL、SDA)是时钟、数据总线控制端,(47)脚是复位控制信号输入端,3.3V电压经RD74、CD66降压后产生一个复位信号,起到复位信号的作用。

VPC3230D(31)~(34)脚和(37)~(40)脚输出的8bit数字视频信号,经FLI2300变频处理后,从(176)、(173)、(170)脚输出模拟的RGB信号。

【提示】模拟信号经VPC3230D、AD9883转换为数字信号,但信号频率没有改变。只有经FLI2300处理后,图像信号行频才变换为31.125kHz,场频才变换为所选扫描方式对应的场频。

KM432S2030C是一个帧存储器,主要通过16位地址线和16位的数据线与FLI2300相连接,它既接收FLI2300处理后的图像信号,也接受从FL12300读出的数据信号。

4.RGB控制电路

所有的显示处理由集成电路TDA9332H(UD2)完成。FLI2300的(176)、(173)、(170)脚输出的模拟RGB信号送到TDA9332H(30)~(32)脚,作为第一基色信号。TDA9332H的(35)~(37)脚输入的是第二基色输入信号(R2、G2、B2),可以是屏显(OSD)信号,也可以是图文电视(Text)信号,但要求输入信号的幅度为0.7V.在IC内部电视信号与屏显信号之间的切换通过叠加功能和快速消隐功能实现。

另外,第二基色输入信号仅受亮度调整控制。

TDA9332H(43)脚是暗电流控制脚(BCL),彩色显像管暗电流调整实际是调整彩色显像管的截止电平,它通过调整三个电子枪的截止电平,使彩色显像管电子束处于不发射电子的截止状态。

5.同步电路与扫描信号处理电路

TDA9332H⑧脚输出的行激励信号由VCO分频产生。为了重显稳定的图像,(24)脚(HS信号)输入行同步信号,在内接时间常数的锁相环(PLL)电路作用下,使压控振荡器的频率与之同步。

行激励信号的频率(fH或2fH由(12)脚(HSEL)接地或开路进行选择。(23)、(24)脚输入的场激励脉冲(VD)和行激励脉冲(HD)的极性TDA9332H内部进行检测,其极性由总线的状态位读出。

第二鉴相环路通过比较VCO提供的基准脉冲和(13)脚输入的行逆程信号的相位,产生行激励脉冲HD,环路的时间常数由IC内部设定。TDA9332H(14)脚输入的行相位校正信号用来补偿由束电流变化引起的水平位移。TDA9332H⑩、(11)脚分别为总线SCL和SDA端。

6.场扫描电路与光栅几何失真校正

TDA9332H①、②脚输出场激励信号,③脚输出东西(E-W)枕形失真校正信号,这些信号均由场频电路产生。场锯齿波发生器需在(15)、(16)脚外接误差非常小的电阻和电容,以确保锯齿波电压幅度稳定。

TDA9332H还具有超高压(EHT)补偿功能,④脚输入的EHTIN信号可以控制水平、垂直几何失真校正电路的输出信号幅度,以维持光栅水平、垂直以及几何失真校正效果不变。TDA9332H的⑤脚为放电保护输入端,防止显像管打火损坏行输出管。