引言

开放式控制器体系结构源于“开放式”的PC(个人计算机) 技术, 目前的开放式运动控制器多为PC+运动控制卡结构, 随着MCU(微控制器) 和DSP(数字信号处理器)性能的增强, MUC和DSP取代PC的趋势日趋明显, 而这种嵌入式的紧凑结构较PC有更广泛的环境适应性。MCU、DSP和PC差异较大, PC环境中的运动控制技术不可能直接向MCU和DSP系统中转移, 基于MCU和DSP硬件平台的运动控制技术的研究十分必要。

设计目标与需求分析

运动控制系统发展方向

在开放式控制器技术的推动下, 运动控制系统由传统的封闭式结构朝着开放、可重构、网络化方向发展。按照《开放式数控系统第1 部分: 总则》(GB/T18759.1- 2002) 的定义, 开放式数控系统有三个层次的开放, 第一层, 系统功能可配置, 人机界面、伺服驱动单元的运动控制接口、逻辑控制单元接口均开放; 第二层, 系统软件体系结构、拓扑结构和应用软件接口开放, 第三方的应用软件能在系统中安装运行并实现互操作性, 且第三方的软件模块可以在拓扑结构不变的情况下对本系统软件模块置换和扩展; 第三层

, 系统实现可重构。国标GB/T 18759.1- 2002 尚未公布可重构的详细内容。运动控制系统是数控系统的一个核心组件, 其技术发展方向和开放式数控系统类似。现代运动控制器联通信息网、逻辑控制网和伺服控制网(接口) 三种网络。

在MCU 和DSP 环境中运动控制技术的研究课题

和PC相比, MCU和DSP采用了哈佛结构, 流水线技术, 超长指令字, 加乘器等提高CPU速度, 并在片上扩展了控制用前向和后向通道外设及通信接口, 在这种环境下, 实现开放、可重构和网络化运动控制功能, 下列研究是必要的:

①体系结构的研究, 以多CPU方式实现复杂的运动控制;

②嵌入式系统中实时操作系统的研究, 解决MCU和DSP控制器系统软件问题;

③MCU和DSP环境中运动控制算法的研究, 解决少资源情况下, 复杂控制算法的实现问题;

④软件模块管理与剪裁技术的研究, 解决通用技术方案的应用针对性问题;

⑤网络通信技术的研究:解决伺服通信网、逻辑控制网和信息网通信问题。

硬件系统设计目标与结构要求

基于MCU和DSP的运动控制技术研究硬件平台的设计目标是为上述研究课题提供硬件系统环境, 以MCU或DSP为核心的商品化运动控制器并不少见,但它们只对用户提供运动控制函数库的接口, 并不是完全意义上的开放, 必须开发运动控制器的硬件研究平台, 并满足下列要求:

①类型与结构化模式要求:CPU选型应是主流的MCU和DSP芯片,结构体系采用单CPU,双CPU流水线模式和层次化结构, CPU可以独立工作, 可以组成流水线模式工作。也可以采用两层结构,上下层分别处理不同实时要求的任务。

②开放性要求:各CPU单元配置计算机通信接口, 如RS232、PCI、CAN、USB 等, 可以方便地实现硬件互联。

③网络化要求:配有伺服单元接口、现场总线接口和以太网接口。

系统设计

运动控制系统硬件结构

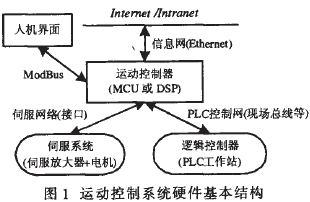

运动控制系统硬件基本结构如图1 所示:

控制器联通人机界面和三种网络。控制器与人机界面的联接多采用开放的工业现场总线ModBus 等;控制器通过以太网接口与Internet/Intranet联接, 实现与管理信息系统的交互;控制器多通过现场总线如CAN、ModBus和RS485等与网络化的PLC工作站通信, 处理控制对象的大量I/O;控制器和高速伺服网络联接, 传送伺服放大器的控制信号, 但该方案技术难度高, 只有少数企业采用专用的高速伺服通信网络实现了伺服电机的组网, 多数方案还是采用的规范化的电机接口, 一个伺服电机的接口如下:

①2路脉冲波形输出, 其间相位差900, 或者其中一路可以作为方向信号( 高或低) ;

②1路AD输出, 一般为±10V,位数为12位或16位;

③2路增量编码器脉冲输入, 一路来自伺服电机,另一路来自执行机构终端;

④3路数字信号输出, 包括伺服使能、正转限制、反转限制;

⑤4路数字信号输入, 包括伺服准备好、左极限、右极限和零位信号;

上述接口电路也可以联接步进电机。运动控制器的内部层次结构如图2 所示:

上层控制器处理复杂控制算法及弱实时任务, 下层控制器处理插补与伺服控制等强实时任务。两个DSP构成双DSP流水线模块, 并行处理复杂实时控制任务。

运动控制系统研究硬件平台设计

主芯片选型

MCU与DSP芯片选型的原则是适用与广泛性原则, 选用的芯片适用于开放式控制器设计并有广泛的硬件与软件资源。三星公司S3C2410A芯片采用ARM920T内核, 主频高达266MHz, 支持WinCE与Linux及μC/OS- II实时操作系统, 可扩展的地址空间1G, 并配有中断、AD、UART、GPIO、触摸屏和TFT接口等片上外设; 德洲仪器公司的TMS320F2812DSP 芯片的主频150MHz, 支持DSP/BIOS和μC/OS- II 实时操作系统, 可扩展的地址空间为1M, 并配有中断、AD、串行接口、事件管理器等片上外设。这两种CPU中,S3C2410A主要用于控制系统管理、监控和复杂控制算法的实现, DSP主要用于伺服电机接口和反馈、滤波等强实时控制算法的实现。

硬件系统配置

整个研究平台硬件配置了三块主机板和一个背板, 其结构如图3 所示:

三块主机板可以单独使用, 也可以组合使用, 它提供了MCU和DSP及双DSP的硬件平台S3C2410A。主机板的USB是Host, 另两块板的USB是Device配置, 另外, S3C2410A主机板和F2812主机板还通过背板有串口通信、GPIO及中断沟通, 可以组合成一个以S3C2410A主机板为

上位机, F2812 - 1和F2812- 2主机板为下位机的双层结构, S3C2410A主机板处理弱实时任务, DSP处理强实时任务;

弱实时任务包括系统监控、模糊与神经网络等复杂控制算法, 强实时任务包括插补计算、数字滤波和PID控制等算法。由此来验证MCU和DSP环境中的算法可行性。

CPU 扩展与外设配置

针对本系统设计要求, S3C2410A主机板原理框图如图4所示。选用两片HY58V561620CT- H, 构成16M×32位RAM空间; 选用两片E28F128J3A150, 构成16M×32 位Flash空间; CPLD选用XC9536, 用于GPIO地址译码和QEP接口的实现, 选用DAC8534A串行16位DAC扩展数模转换接口, 采用CS8900A 以太网芯片扩展网络接口。

F2812-1主机板原理框图如图5所示, 选用IS61V5126, 扩展256KROM空间, 选用AM29LV800BT扩展512KFlash, 选用XC95144XL进行GPIO地址译码, 选用AN2131Q作USB Device的扩展, 在McBSP串口上扩展16位DAC8534A用于伺服的速度与力矩控制。特别的, F2812提供了完善的伺服电机接口, 它有两个事件管理器, 每个事件管理器包括两个通用计数器, 三个比较/PWM单元, 三个捕捉单元, QEP通道。PWM和通用计数器配合可用作伺服控制器的位置控制模式输入, QEP通道可用作伺服电机的位置编码器脉冲输入, 执行器终端的编码器信号通过CPLD扩展QEP输入。

F2812-2主机板原理框图如图6所示, 为了验证多电机的并行控制算法, 在F2812-1主机板的基础上, 用双口RAMIDT70V25将两个CPU联接起来, 形成了一个对称结构。按目前板上的电机接口配置, 每块板可接两路全闭环伺服电机, F2812-2主机板可接四路全闭环的伺服电机。

结论

选用S3C2410A和F2812作运动控制系统的嵌入硬件研究平台, 组成一个多CPU的双层控制器结构,既可以单独进行单MCU和DSP环境中的运动控制算法研究, 又可以进行多CPU平行模式的复杂运动控制系统研究。系统简练、可靠, 符合运动控制器的开放式、可重构和网络化的发展方向。

本文作者创新点:针对嵌入式运动控制器发展趋势,设计实现了一个开放式、可重构、多CPU的运动控制器硬件平台, 该平台可用于复杂运动控制系统的研究。