摘要:德州仪器TI推出的八核DSP芯片TMS320C6678是目前基于Keystone架构的最高性能的DSP器件,是市场上应用广泛的C6455高端处理平台升级的理想选择。本文主要研究了C6678 DSP程序的各种单核加栽和多核加载的几种模式,主要用到多核boot技术,对EMIF16 FLASH boot引导模式、主机(PCIe接口)引导模式、I2C引导模式、SRIO引导模式、网络引导boot引导模式的方法做了研究,对TI的高性能多核架构DSP芯片的程序加载提供了有效的参考帮助。

近年来,以数字信号处理器(DSP)为基础的通用信号处理模块的研制受到人们的重视,DSP技术广泛应用于雷达、通信、图像处理等领域。随着声纳、雷达、高清视频以及嵌入式机器视觉等需求不断攀升,多核DSP的应用已成为满足发展的重要途径。由于DSP系统稳定运行起来后,在实际的应用中都要脱离仿真器件,实现系统的自动加载,尤其是多核DSP加载过程中,不同于多芯片间的加载方式,需要实现核间的调度,数据协同处理,因此多核启动的加载方式需要做具体研究。

TMS320C6678 DSP是TI最新发布的一款基于KeyStone架构高性能的超长指令字(VLIW)架构芯片,片内有8个内核,每个核频率为1.25 GHz,单核每秒高达40 GB MAC定点运算和20 GB FLOP浮点运算能力,工作速度可达10GHz。与目前应用较为广泛的TMS320C6455DSP,为单核1.2GHz工作,定点处理能力为9600M MAC。可见C6678的处理能力要远强于C6455。针对C6678多核协同处理特性,本文以自定义的双6678板卡平台为基础,深入研究C6678的多种加载方式,对EMIF16 FLASH boot引导模式、I2C引导模式、SRIO引导模式、网络引导boot模式做了分析和说明,主机(PCIe接口)引导模式、HYPERLINK引导模式和SPI引导模式的使用,本文不做说明。

1 多核加载方式论述

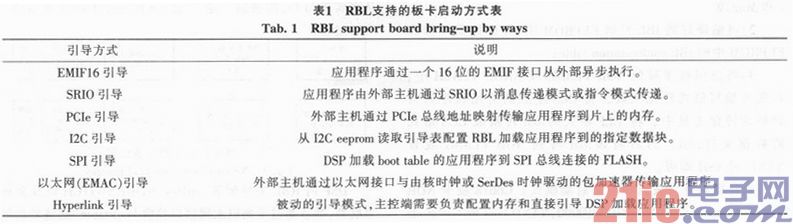

在C6678的片内地址空间0x20800000到0x20B1FFFF间集成了一块128K的内部ROM程序,又叫做RBL(ROMBoot Loader),Rom code是C6678出厂时固化在Rom中的,用户不能改变,在DSP复位或上电时实现将DSP代码从外部接口读入到内部高速ram。启动过程可以大致分为主机引导和内存引导启动,在内存引导启动过程代码从一个外部内存的加载初始应用程序到内部的内存来执行。如果主机模式,启动程序配置DSP在被动状态,等待代码将DSP应用程序程序由外部主机写入ram开始执行。为适应不同的系统要求,RBL提供了几种启动的执行方式。不同的引导方式如表1所示。

2 多核boot预处理

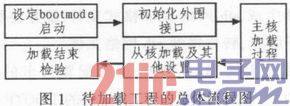

C6678有8个核,采用基于KeyStone架构的中断控制器、核间通信寄存器以及合适的通信拓扑结构实现多核间的通信,core0为主核,其它7个核可以统一执行相同的Romcode代码,也可以不同,或者根据核号(即DNUM)进行不同程序的分支。对于core0来说,它主要是读取DEVS TAT寄存器的加载模式,并根据当前加载模式进行一些接口的初始化和PLL的配置,还要根据加载模式决定是否搬移数据。对于其它的7个核来说,它们主要是挂载IPC中断,然后进入IDLE状态等待core0发过来的中断。中断一到,就跳到入口地址开始执行程序,待加载工程总体流程如图1所示。

代码读入前要根据不同的boot方式进行转换格式,转换工具是将各核的.out文件转换成.dat或.bin文件,也有网络boot时要转换成.eth格式的文件来传送,不同的转化方式在各自的boot说明中详细阐述。无论哪一种启动方式,首先要boot起来core0之后再引导其他的从核,重点是从核在boot启动时通过host向DSP写了MAGIC_ADDRESS并触发IPC中断,DSP跳转到BOOT_MAIGC_ADDRESS所指向的地址执行程序。

3 C6678 EMIF flash boot

3.1 core0加载

C6678的EMIF16加载是一种直接从Nor Flash(必须挂在CE2空间:0x70000000)加载core0的模式,不需要I2CEEPROM的参与,由Rom code初始化EMIF16接口,由于EMIF16外接Nor Flash是一种XIP器件,因此直接跳到Nor Flash的起始地址处开始执行。

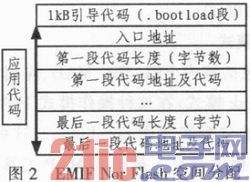

为了将Nor Flash中的代码搬移到C6678的core0的L2SRAM中,需要在core0的待加载工程中编写引导代码,此引导代码的作用就是将core0的代码按段加载到内存中,最后跳到入口地址处开始执行。引导代码放在L2 SRAM的前1KB空间,并烧写到Nor Flash的前1KB空间,应用代码放到1KB后面,生成.out文件编写转化工具生成.dat文件,如图2所示Nor Flash代码格式:

3.2 core0加载其它核

在多核加载过程中,core0是主核,corel-core7是从核,由core0加载从核,具体步骤是:

1)上电后,core0完成程序加载,并跳到入口地址开始执行程序。

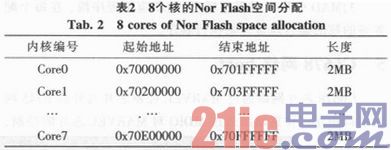

2)在core0主程序中.core0从Nor Flash中读取corel的代码,并按段加载到core1的L2 SRAM,然后将core1程序的入口地址写到core1的BOOT_MAGIC_ADDRESS,最后向core1发送IPC中断,其它核的加载过程一样。各个核的Nor Flash空间分配如表2所示。

在将c_int00地址写到magic address时,注意需要确保写的是全局地址,如当程序放在L2时,c_int00地址应该转换为0x1n8xxxxx,其中n为coreID.

4 C6678 I2C boot

C6678的I2C boot是通过I2C总线读取挂载在总线上的eepromm中的IBL读取参数表配置RBL加载应用程序到的指定数据块。可以操作主I2C模式或从模式,在主模式的DSP读取带有镜像文件的I2C从设备。在从模式,DSP为I2C连接的从设备,主设备大多是另一个DSP或FPGA。

4.1 单核启动模式

单核启动包括:RBL、IBL、应用程序。对于I2C启动,需要做的主要有4步:

1)编译IBL:不同版本的IBL,其目录下的内容有些差别。编译IBL需要的工具有TI CGEN eompiler CGT_C6000_7.x和MinGW。

2)将编译好的IBL写到EEPROM中,并根据需要修改EEPROM中的IBL configuration table;

3)将应用程序写到NOR FLASH或NAND FLASH中:

首先要编写格式转化工具,将CCS生成的应用程序拷贝到格式转化工具中,将ELF格式的.out转换成CCS格式的数据文件.dat,然后将该.dat写到NOR FLASH或者NAND FLASH即可。

4)将拨码开关拨到相应的启动模式。C6678板卡NORboot的bootmode[]=101000100010000,NAND boot的bootmode[]=101010000010000。

4.2 多核启动模式

多核启动包括核内RBL、IBL、MAD、应用程序。

采用pre-link模式:在这种操作模式下的MAP工具为应用程序段做地址分配和调用pre-linker。这种模式适合使用在多核,是应用程序开发人员想要MAP工具协助地址分配,使多核应用之间的通用代码共享。

MAD引导的多核装载的过程有以下几个步骤:

1)在启动时候,DSP设备将运行ROM引导装载程序,将加载并运行在i2c eeprom上载好的IBL。

2)IBL将下载MAD镜像文件从tftp服务器(MAD文件也可以存数在板上的NOR/NAND FLASH中)到DDR中。给IBL配置了一个执行程序的入口地址,在非MAD引导的情况下,此地址将是运行程序下载的入口地址,在MAD引导情况下,IBL配置为跳转到MAD Lader的入口地址。

3)MAD引导装载程序情况,装载应用程序段,在每个配置好的核的运行地址开始执行程序。

5 C6678网络boot

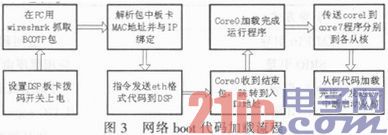

C6678芯片网络通过MARVEL控制芯片与外部RJ45网络接口相连,注意增加通过MDIO对MARVEL芯片的控制,从而实现与PC的通信。建立C66 78的网络boot主要有图3所示过程。

DSP内RBL主要配置SerDes,SGMII,SWITCH以及多核导航器,准备通过千兆以太网接口接收boot table。这些最初的配置是通过查询与启动模式相关的DEVSTAT寄存器和引导网络boot的parameter table。在启动模式选定后,PA子系统的时钟主要参考main PLL的参考时钟或Ser Des参考时钟。

1)使用arp指令查看网络缓存区链接状态,arp-a检测网口外接的设备。

2)使用hex6x.exe将out文件生成hex文件:要有*.cmd文件和hex6x.exe和*.out文件。

3)编译生成.eth网络boot格式文件:最好将编译工具放到本目录下编译,转化得到.eth网络文件。

4)获取板卡的MAC地址:正确配置板卡的拨码开关。

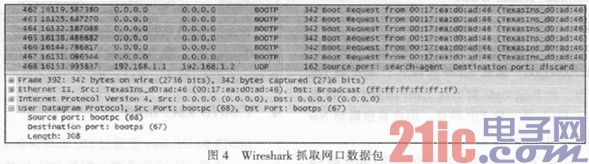

配置正确以后PC就能收到板卡发出的BOOTP包(3 s周期),设置C6678的bootmode[]=010000100111000。查看板卡的MAC地址:通过wires hark抓包获取板卡板的MAC地址。

5)传输boot文件:MINGW环境里面运行指令,绑定板卡的MAC地址和IP,设置板卡IP地址为192.168.1.2,PC端的地址为192.168. 1.1。文件传输指令pcsendpkt.exe simple.eth 192.168.1.2。发送文件到板卡内存,传输文件成功后可以板卡停止向PC发送MAC地址,并且可以看到PC向板卡利用UDP协议传输DSP Core0的代码,Wireshark抓取网口数据包结果如图4所示。

将Core0的代码存到DSP的内存,此时Core0仍处于boot load的EMAC加载模式,当发送完毕代码后,向Core0发送结束包.Core0根据EMAC加载协议,当收到该包后则从加载模式跳转为正常模式,PC指针从指定的程序入口地址处开始运行。

6)在core0加载的程序中编写core1到core7的加载程序,通过网口读入coreN各个核的代码程序到对应的RAM中,如果7个从核的代码相同,只用读入一次从核心代码,加载到7个核中,0核像7个核发送IPC中断触发运行程序。观察程序跳转地址到设定的地址处,验证程序运行结果。

6 C6678 SRIO boot

C6678支持的SRIO协议为2.1版本,link rate速率即1.25G,2.5G,3.125Gbit,使用4x模式。SRIO协议规定有两种传输方式:Direct IO与Message方式。当DSP处于SRIO bootload模式时,将代码直接写入DSP内存并中断.DSP立即从boot模式跳转到正常模式,执行加载的代码.

1)程序文件格式的转换:

①使用代码转换工具hex6x.exe转换ELF格式的out文件成为十六进制格式的boot table文件。

②使用Bttbl2Hfile.exe,hfite2array.exe将boot table文件转换为一个DAT格式文件。

③复制生成文件到\srioboot_example\src,使boot image链接到DSP的启动程序中。

2)DSP boot过程:DSP boot工程使用多核程序包的BIOS支持库来初始化DDR,它首先从SRIO连接的DSP中通过SRIO将DDR的初始化程序的代码读入到Core0的L2RAM中,然后写入DDR初始化引导程序的入口地址到core0的boot magic address中。在DSP上运行的RBL检测到core0发起的入口地址,并跳转开始启动初始化DDR。DDR的初始化代码在初始化DDR正确后将继续校验SRIO boot magicaddress,SRIO boot引导流程如图5所示。

然后从DSP将由SRIO把应用程序引导到本地的DDR内存启动板卡,写入的应用程序的入口地址到core0。Core0开始启动和打印启动信息,并通过write_boot_magic_number()和一个IPC中断发送到其它核心,写入入口地址启动其它从核,程序会跳转到其它核上运行的写boot地址命令开始启动,每个核心将写入0xBABEFACE到对应的SRIO boot magicaddress。

3)板卡SRIO boot:板卡上包含两片C6678芯片,SRIOboot。两片C6678通过4xlane差分线互联,使用RS-232总线连接到PC的串行端口,板卡设置boot模式,C6678_A的bootmode []=100000101011000,C6678_B的bootmode []=100000101011100。这将设置引导板从SRIO启动,参考时钟频率为312.5 MHz,数据速率3.125 GBs和lane设置4x端口,在1GHz的系统时钟。

打开超级终端或TERA终端连接,设置波特率115200,数据8位,无奇偶校验,停止位和流量控制,连接主机的CCSv5,加载和运行srio boot_example_evm66xxl.out程序。CCS控制台将显示以下消息:…[C66xx_0]Transfer boot code via SRIO successfully

超级终端会显示以下消息:SRIO Boot Hello World Example Version 01.00.00.01;Booting Hello World image on Core0 from SRIO … … Booting Hello World image on Core7 from Core 0

7 结 论

TMS320C6678是8内核的DSP,主要实现了系统自动加载boot load程序,支持的多种加载方式:主要有EMIFFLASH加载、网络EMAC加载,以及SRIO加载和I2C加载。多种加载方式能为实测项目应用中达到更高的效率,在数字信号处理系统中多核DSP的发展必然成为一种趋势,多核间的有效加载更直接影响到项目的整体特性,按照该设计思路编制的boot load方法已在TMS320CC6678+FPCA的CPCI处理卡中得到应用,应用的高端处理平台可使用于航天领域、船舶领域、无线平台和高速图像处理领域等,多核DSP系统能很好的复位及快速完成多核间的加载,系统运行稳定可靠性较高。