介绍了一种基于DSP+FPGA结构的小波图像处理系统设计方案,以高性能数字信号处理器ADSP—BF535作为核心,结合现场可编程门阵列FPGA,实现了实时数字图像处理。

小波分析是近年迅速发展起来的新兴学科,与Fourier分析和Gabor变换相比,小波变换是时间(空间)频率的局部化分析,它通过伸缩平移运算对信号逐步进行多尺度细化,最终达到高频处时间细分和低频处频率细分,能自动适应时频信号分析的要求,从而可聚焦到信号的任意细节.解决了Fourier分析不能解决的许多问题。

目前许多小波算法的软件实现已经很成熟了,但是很难达到实时性的效果。而在硬件方面,随着数字信号处理器(DSP)和现场可编程门阵列器件(FPGA)的发展,采用DSP+FPGA的数字硬件系统显示出其优越性,可以把二者的优点结合在一起,兼顾速度和灵活性,因此DSP+FPGA结构正愈来愈得到人们的重视,应用的领域也越来越广泛。

DSP+FPGA系统最大的优点是结构灵活,有较强的通用性,适合于模块化设计,从而能够提高算法效率;同时其开发周期较短,系统容易维护和扩展,适合实时信号处理。所以本文介绍的系统设计就是基于DSP+FPGA结构的小波图像处理系统。

1 图像处理系统的组成

1.1 系统整体硬件构架

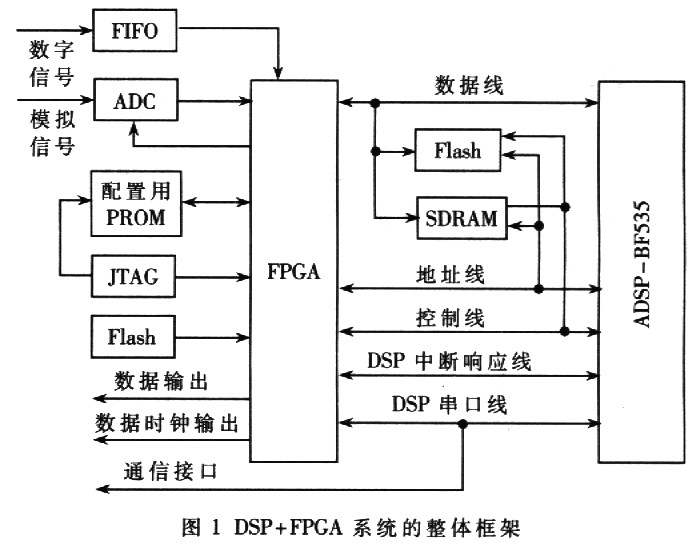

DSP+FPGA系统的核心由DSP芯片和现场可编程门阵列FPGA以及外围的辅助电路,如存储器、先进先出(FIFO)器件及Flash ROM等组成。外围电路辅助核心电路进行工作。DSIP和FPGA各自带有RAM,用于存放处理过程所需要的数据及中间结果。

Flash ROM中存储DSP执行程序和FPGA的配置数据。FIFO器件则用于实现信号处理中常用的一些操作,如延时线、顺序存储等。系统方案考虑了系统处理的实时性、硬件系统的规模及系统调试的难度等因素,其整体框架如图l所示。

1.2 处理器简介

ADSP-BF535(简称BF535)是美国AD公司和Intel公司于2001年底联合推出的一款定点DSP,属于Blackfin系列产品。BF535具有RISC指令结构,运作高效,性能优异,主频最高工作在350MHz。有两个40位的乘加器和两个32位的算术逻辑单元,四个8位的视频处理单元,十六个地址寻址单元。

DSP内部集成了308KB的RAM,并有丰富的外部接口,如SDRAM、PCI、USB、SPI、同步和异步串口等。芯片内部设计了“看门狗”和多种定时器,可充分满足软件工程的稳定性设计要求。而且BF535可动态地控制电压输入,调整运行频率.减少芯片功耗,十分适合于移动产品的设计。

1.3 外部存储器的设计

Blackfin DSP的结构体系将存储器构造成统一的4GB地址空间,用32位地址寻址。包括内部存储器、外部存储器、PCI地址空间和I/O控制寄存器在内的所有资源,在这个统一的地址空间中独自占据各自的一段。

外部存储器通过外部接口总线进行读取。该接口提供一个无缝连接,最多可接4个SDRAM和4个异步存储装置(Flash、EPROM、ROM、SRAMq及存储映射I/O装置。

存储器的设计首先要考虑存储器的速度、类型、容量是否能满足运算要求以及性价比如何。本系统中扩展了外部存储器,用到了SDRAM(用来在算法运算过程中对图像数据的缓存)。与PCI33兼容的SDRAM控制器最多可以设置为四个地址空间相连的SDRAM存储块,每个存储块的大小可为16~128MB,所以最高可访问512MB的RAM。每个存储块都可以独立配置,并且与邻近块连续而不必考虑存储块的大小和位置。

这使得内核可以把所有SDRAM都看作有单一、连续的物理地址空间。本系统中ADSP-BF535与SDRAM的接口如图2所示。

异步存储器接口选用了双端口RAM作为图像数据从FPCA到DSP之间的传输,通过对DMA控制寄存器的设定,图像数据以DMA方式向DSP传输。选用F1ash作为程序存储器。BF535与Flash的接口如图3所示,系统上电后程序从Hash以DMA方式自举到内部程序RAM中,应用程序在内部程序RAM全速运行。

1.4 模/数转换部分

高速A/D变换对采集到的信号数字化后,将模拟图像信号转换为数字图像信号,存入图像存储器中。A/D变换器采用AD9042,其最高采样频率可达40MHz。精度为12位,输入信号范围为±2V。

1.5 通信接口部分

BF535的UART是与PC机的标准异步串口兼容的全双工外设,它有两个相互独立的uART,UART在串行和并行格式之问转换数据,通信接口部分由一个RS422和一个RS232串口组成。中心控制器通过串口发送指控指令,实时数字图像处理系统对目标处理数据进行修正和规范化处理,并迭出符台规定格式的处理数据。

1.6 FPGA在系统中的使用

系统采用Xilinx公司的SpartanⅡ系列的FPGA芯片,并且用FPGA实现FIFO及扩展串口的功能。时序控制由现场可编程门阵列FPGA实现,其实现的主要功能有:(1)产生DSP访问的地址译码与控制。(2)产生DMA端口访问DSP所需的控制信号。(3)产生OSP的复位信号。(4)产生A/D转换器的转换控制时序,包括SCLK(串行时钟)和CONV(转换控制)。(5)产生串口的接收帧同步信号。

系统使用FPCA可以减少外围芯片的数量,而且可以比较方便地修改设计方案,为以后系统的扩展提供了空间。

2 二维小波分析在图像处理中的应用

数字图像处理的目的就是对数字化后的图像进行某些运算或处理,以提高图像的质量或达到人们所要求的预期结果。小波变换用于图像处理是小波变换应用比较多的领域之一。由于图像是二维信号,因此,应用的小波分析工具是二维小波变换。小波变换在图像处理上的应用主要是将空间或时间域上的信号(数据)变换到小波域上,成为多层次的小波系数。然后根据小波基的特性,分析小波系数特点,针对不同需求,结合常规的图像处理方法或更符台小波特点的方法来处理小波系数,再对处理后的小波系数进行逆变换,得到所需的目标图像。

2.1 二雏离散小谊变换的一般形式

二维离散小波变换的一般形式可以表达为:

2.2 二维图像的小波分解与重构

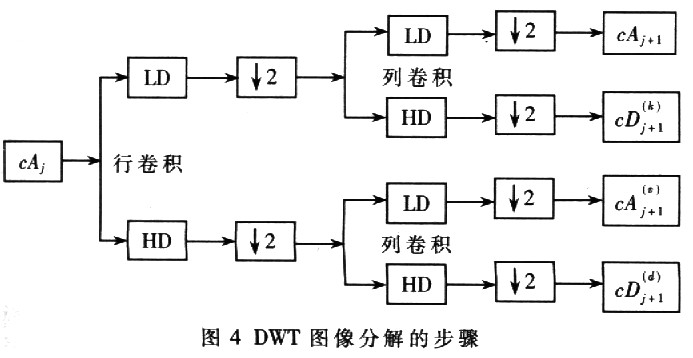

从一幅N×N的图像开始,N是2的幂。若j=O,尺度2=2°=1,即为原始图像的尺度,j的值每次增大都使尺度加倍,而使分辨率减半。图像可以依据二维小波按如下方式扩展:在变换的每一层次上,图像都被分解为四个1/4太小的图像.这四个图像中的每一个都是由原图与一个小渡基图像的内积后,再经过在x1、x2方向都进行了两倍的间隔抽样后而生成的。

图4为分解的实际计算框图,图中cA为低频系数,cD(h)、cD(v)、cD(d)为高频系数,LD为低通分解滤波器,HD为高通分解滤波器,向下的箭头表示隔行或隔列抽样,保留偶数行或列,行列以O开始。

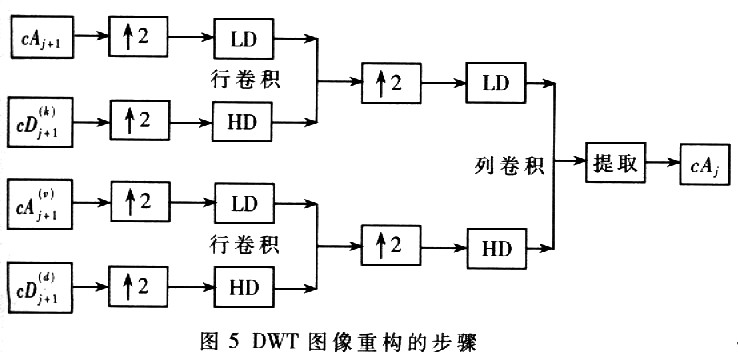

重构的过程是分解的逆过程,与分解的过程类似。图5为DWT图像重构的实际计算框图,其中向上的箭头表示示插样或行插样,即在奇数列或奇数行插入O值。

2.3 小波算法在BF535上的实现

图像处理的小波算法在BP535上实现。AD公司提供了一套完整的ADSP—BF535软硬件开发工具,包括仿真器、评估板和Visual DSP++开发环境。小波算法在BF535上实现的主要步骤如下:

(1)用C语言编程实现算法。

(2)使用Visual DSP++的C/C++编译器,将C源程序编译成目标文件。

(3)根据产生的目标文件,分析结果及源程序结构,并优化源代码。

(4)应用ADSF-_BF535评估板进行运算时间评估。

(5)重复上述步骤,直至达到系统实时性的要求为止,然后下载到目标板。

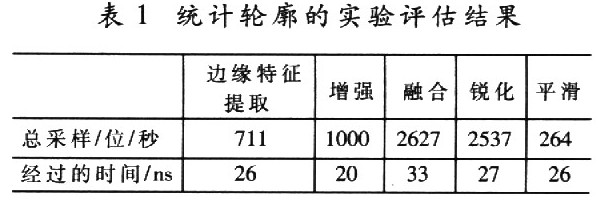

在实验中,甩小波算法对256×256像素的图像进行边缘特征提取、增强、融合、锐化、平滑等处理,算法分析结果如表l所示。可得出结论,使用BF535可以实现小波图像算法,并且其速度满足实时性的要求。

2.4 小波变换在数字图像处理中的应用

小渡变换在图像处理中的应用主要有图像压缩、图像的去噪、图像的增强、图像分割、图像特征描述和图像重建等。

本文介绍了应用数字信号处理器ADSP—BF535和现场可编程门阵列FPGA,设计了小波图像处理系统,并用ADSFl_BF535实现了小波算法。分析DSP片上资源和运行时间的结果表明,其速度可满足实时性的要求,可以在本系统中使用小波算法来处理实时图像信号,为硬件系统的设计提供了保证。小波分析由于具有良好的时频局部化性能,已经在信号分析、图像处理、语音合成、故障诊断、地质勘探等领域取得一系列重要应用。

而且各种快速有效的算法也促进了小波分析在实际系统中的应用。由于DSP速度越来越快,成本越来越低,FPGA的容量越来越大,使得DSP+FPGA组成的系统成为解决系统设计的重要选择方案之一,应用领域非常广泛。