0引言

在现代导航计算机系统朝着微型化发展的过程中,采用高性能数字信号处理器和可编程逻辑器件方案实现的导航计算机系统有着很高的性能优势。在本课题组研制的基于浮点型DSP和复杂可编程逻辑器件(CPLD)结构的嵌入式微型导航计算机系统中,DSP负责导航解算任务,CPLD用来辅助DSP对外围通信接口芯片进行控制,以减少DSP的控制任务,使其更专注于导航任务的解算。采用CPLD可以提高导航计算机控制和配置的灵活性,便于系统的升级和更新,使接口配置更灵活,适合于不同的传感器和便于应用于采用多传感器信息融合的组合导航系统中,充分发挥DSP的计算能力,提高导航性能。此嵌入式导航计算机系统中CPLD采用的是Xilinx公司的XC95144,该器件支持在系统编程(InSystemProgramming)和扩展的IEEEStd1149.1JTAG边界扫描测试规范。JTAG标准作为一个测试规范,已被多数可编程逻辑器件采用。对于该芯片的一般编程方法是,通过Xilinx公司提供的下载线缆将PC机并口转接至其JTAG端口,使用PC机下载软件实现对其软件更新。由于JTAG口的信号特点,下载线缆不能太长,否则会导致信号失真;此外,在系统投入使用后,如果需要对软件进行更新升级,采用这种线缆方式必须将系统的外壳打开,不便于系统的维护更新。本文通过对JTAG接口特性的研究,提出了一种采用UART串行通信进行软件更新的方案,对基于DSP接口控制的CPLD器件实现了软件更新,使采用JTAG口进行编程的PLD器件可以实现远端更新和升级。

1JTAG接口原理

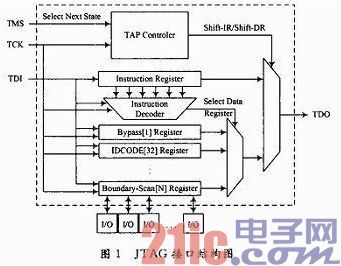

JTAG是IEEE的联合测试行动小组(JointTestActionGroup)提出的测试标准,此标准最初是用来解决因芯片集成度和板级器件密度越来越高带来的测试问题。现在这一标准已被大多数器件厂商采用并设计到芯片电路中,用以支持其器件在系统调试或编程功能。对于本文所用的CPLD器件,其JTAG接口的结构如图1所示。

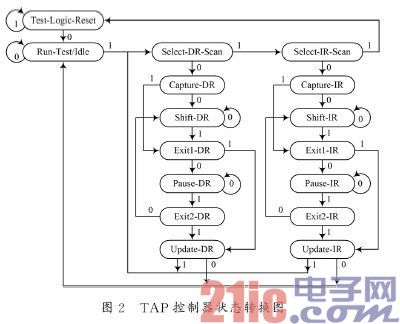

JTAG 标准定义了4个基本单元:测试访问端口TAP(TestAccessPort)、数据寄存器、指令寄存器和TAP控制器。TAP端口包含了4个JTAG信号:测试时钟输入引脚TCK,测试数据输入引脚TDI,测试数据输出引脚TDO和测试模式选择引脚TMS。数据寄存器主要包含2种:BYPASS寄存器和 BSR(BotlndaryScanRegister)寄存器,其中BSR由BSC(BotmdaryScanCell)串联而成,正是通过BSC扫描链电路,来自于TDI上的CPLD配置信息便可移入到芯片内部,从而实现对器件的擦除与编程功能。TAP控制器其实是一个包含16个状态的状态机,它控制着测试访问口、指令寄存器和数据寄存器。TAP控制器状态转换图如图2所示。

TAP控制器的状态由TMS和TCK两信号控制。当需要将TDI上的数据移到指令寄存器中时,可使TAP控制器进入Shift-IR状态;当需要将TDI上的数据移到数据寄存器中时,可使其进入Shift-DR状态。通过 TAP控制器的状态转换,可将CPLD的配置信息移入到其内部逻辑中。

在基于PC的编程方法中,CPLD的配置信息文件存储在PC里,在PC中运行的下载软件不断读取器件的配置信息,并通过其并行接口模拟JTAG测试端口的时序和逻辑,从而实现其软件更新和下载。本文将采用导航计算机系统中的 DSP来实现这种编程方法:CPLD的配置文件通过DSP的UART串行口发送给导航计算机系统,然后由DSP解析并执行配置文件中的指令,通过DSP的 I/O口模拟JTAG端口信号行为,来实现对CPLD器件软件更新的功能。基于这种方案可以实现采用普通的串行口方便地对CPLD进行远端编程和更新。

2CPLD的JTAG接口编程的硬件设计

为实现本文提出的导航计算机系统中基于DSP的CPLD器件软件更新串行方案,首先需要在硬件方面解决如下3个问题:

(1)导航计算机系统所用DSP至少要有4个空余的I/O口,分别用于模拟CPLD的4个JTAG信号时序信号。

(2)导航计算机系统必须包含支持一个UART通信接口,用于接收CPLD的配置文件。此UART接口不能由CPLD参与控制,以避免CPLD某次编程失败后,该UART通信口不再可用的问题。

(3)导航计算机系统应保证足够的CPLD配置信息文件需要的存储空间。

本文所用DSP为TI公司的TMS320C6713B芯片,该款DSP支持16个通用输入输出口(GPIO)。在本导航计算机系统中,有12个GPIO口已被占用,多余的4个GPIO口可用来连接CPLD的4个JTAG信号引脚。

TMS320C6713B 本身并不支持包含UART通信接口,其片上外设中包含2个多通道缓冲串行接口(McBSP),McBSP接口支持全双工串行通信,只是收发数据需要独立的收发帧同步信号。根据TI公司提供的应用技术报告,经过对软件或硬件进行改造设计,McBSP接口可以支持UART通信标准。软件修改方法是通过将 McBSP接口配置成通用I/O接口来模拟UART时序;硬件修改方法是将McBSP接口配置在串行口模式,McBSP接口中接收帧同步信号FSR来自于 UART的发送数据线Tx,在检测到Tx的下跳沿时,McBSP内部开始采样接收数据,之后Tx的下跳沿将被忽略直至下一个字节的起始位再次触发内部帧接收新的数据;发送帧同步信号FSR由McBSP电路在发送UART数据起始位时产生。本文采用硬件修改和过采样软件措施,将一个多通道缓冲串行接口 McBSP0设计成了支持UART通信标准的接口。

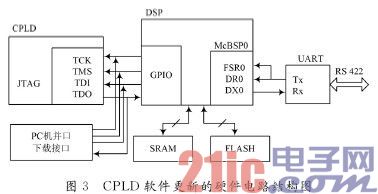

本导航计算机系统使用的CPLD配置信息文件是串行矢量格式(SVF),可以在 Xilinx软件开发平台ISE上生成。SVF是一种用来描述IEEE1149.1(JTAG)总线操作的规范,包含了编程需要的指令和数据,描述了 TAP测试访问端口状态图中各状态之间的扫描操作过程和行为。由于SVF文件是ASCII格式,所以占用的存储空间比较大,可以将其转换为一种更简洁和紧凑的二进制格式:XSVF文件。对于本系统所用CPLD器件而言,仅对其进行编程操作时,XSVF文件大小为129720B,加上擦除和校验操作后,XSVF文件大小为259533B。根据上述分析,本文设计的嵌入式导航计算机系统中通过UART接口对CPLD器件进行在系统软件更新的硬件电路结构如图3所示。

图 3中,UART通信口由DSP片上多通道缓冲串行口McBSP0实现。为了存储通过UART口接收到的包含CPLD配置信息的XSVF文件,本系统外扩了一片512kB的SRAM。FLASH芯片用来存储导航计算机系统升级固件和应用程序。CPLD的JTAG口直接与DSP空闲的4个GPIO口相连,为了提高CPLD器件编程的灵活性,在本系统中保留了连接PC机并口的CPLD程序下载接口。

3CPLD的JTAG接口编程的软件设计

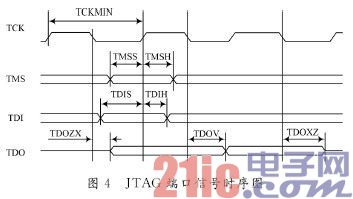

在硬件设计的基础上,为实现通过DSP的GPIO口模拟JTAG信号时序逻辑来对CPLD进行软件更新,需严格按照JTAG标准中的端口信号时序要求。对于本文所用的CPLD器件,其JTAG端口信号时序关系如图4所示。

由图4可见,对于JTAG口时序逻辑需考虑如下3项内容:

(1)JTAG接口要求一个最小时钟周期TCKMIN。

(2)JTAG接口在TCK的上升沿采样TMS和TDI信号。因此在TCK上升沿之前,TMS和TDI要具有最小分别为TMSS和TDIS的建立时间,同时在TCK下降沿之后要保持最小分别为TMSH和TDIH长的时间。

(3)在TCK的下降沿,JTAT接口输出新的TDO值,并保持至少TDOV长的时间。

本文所用CPLD的JTAG端口时序参数要求如表1所示。

在本文设计的导航计算机系统中,DSP的工作主频为200MHz,利用TI公司提供的库函数,由该DSP的GPIO口模拟的时钟频率最大不超过3MHz,可以满足表中TCKMIN参数对应的最大10MHz的要求。对于建立和保持时间等参数要求,可通过软件延时或定时器实现。由于在本系统的应用中,DSP在上电期间专注于CPLD的软件更新,所以本文将采用软件延时来实现这些参数要求,设计的JTAG口信号电平驱动函数模块代码如下:

利用上述代码,模拟实现的JTAG时钟信号频率为367.6kHz。

DSP 在配置CPLD器件时,不断从存储在SRAM里的XSVF文件中读出指令和参数,并根据不同的指令执行对应的操作。根据功能特点,XSVF文件中的指令主要包括:状态转移、指令移入、数据移入或移出和空闲等待这4类指令。状态转移指令用于控制TAP状态机进入与下条XSVF指令操作对应的状态中,在 XSVF文件中,图2中的每个状态对应一个字节的编码;指令移入用于将TDI上的指令代码移入对应的指令寄存器;数据移入或移出指令可将TDI上的数据移入CPLD器件内部逻辑中,同时可以捕获从TDO上移出的数据;空闲等待指令可提供移进CPLD擦出指令或数据后等待内部逻辑成功响应需要的时间。

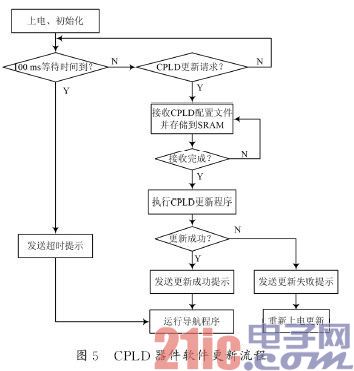

在上述设计的基础上,设计通过串行方式的CPLD更新流程如图5所示。

图 5中系统首先通过DSP的串行口接收CPLD的编程配置文件,接收完配置文件后,可在35s之内完成CPLD的软件更新。在实际应用中,应用本文的更新方案,可根据需要很快实现不同的系统配置方案,如可选择INS和GPS组合。或与地磁组合等,无需重新更改硬件,便可配合多种传感器,克服了通过常用PC机与下载线缆进行软件更新的弊端,避免了反复打开、组装系统等一系列的繁琐工作,提高了现场调试的效率,从而提高了导航计算机系统的适应性。

4结语

通过硬件和软件设计,本文实现了基于DSP的CPLD器件软件更新的串行方式。目前已在本课题组研制的基于DSP和CPLD 的嵌入式导航计算机系统中进行了成功应用。该串行口更新方式相对常用的基于PC并口的编程方法,解决了并口转JTAG口的下载线缆过长而不能可靠对 CPLD更新的问题,同时可以实现CPLD器件在系统的远端更新,避免了繁琐的现场拆除板卡进行软件更新和升级的弊端,提高了系统的可维护性。另外,通过外加网络接口,应用本文设计的软件更新方案,还可实现CPLD器件的远程更新。本文的设计对于嵌入式导航计算机系统的更新和升级具有较好的适用性,提高了系统应用的灵活性,可以应用到具有不同配置的多种导航系统中,也可以在一种导航计算机系统中通过对CPLD的不同配置来适应不同的传感器和接口。