引言

扩频接收机载波的同步包括捕获和跟踪两个过程,载波捕获即多普勒频移的粗略估计通常包含在伪码同步过程中,而精确的载波相位及多普勒频移则通过FLL(锁频环)和PLL(锁相环)跟踪来实现。锁频环直接跟踪载波频率,而锁相环则直接对载波相位进行跟踪。锁相环具有较高的跟踪精度,但对通信链路干扰的容忍能力差,特别是受载体动态引入的多普勒频移影响较大;而锁频环具有较好的动态性能,但跟踪精度较低。载波跟踪环的跟踪精度决定了最后定位测量的精度。常规接收机中载波跟踪是在数字延迟锁定环对伪码相关解扩的基础上,通过科斯塔斯环(PLL的一种)重构载波相位解调BPSK数据实现的。当多普勒频移高于±40kHz ,多普勒频率一次变化率为4kHz/s ,二次变化率为200Hz/s2时,接收机的PLL将不能稳定工作。由于在系统设计中,多普勒频移远小于这一极限值,另外,锁频环鉴别器需要两组相关积分采样点用于计算频率差值,并且这两组采样值应该在同一个数据位时间区间之内。系统中,由于积分时间与调制数据位宽度相同,每次得到的相关采样值将位于不同的数据位区间内,不适合使用锁频环,故只采用科斯塔斯环完成载波频率和相位的跟踪。

环路原理

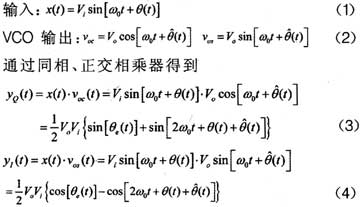

科思塔斯载波跟踪环由载波鉴相器、载波环路滤波器和载波NCO组成。其结构原理图如图1所示。

环路实现

载波NCO的FPGA设计

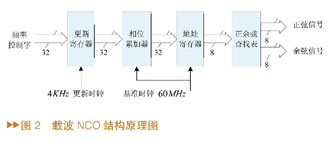

载波NCO是载波跟踪环的重要组成部分,它的主要功能是产生本地复制载波信号。载波NCO主要由相位累加器、地址寄存器和正弦查找表构成。结构原理如图2所示。

载波NCO设置有频率控制字输入口,相位累加器对输入的控制字进行累加,累加结果的高8位作为查询表的地址,通过查询预先存设的正余弦表,输出两路信号,其中一路与载波同相,另一路与载波正交。载波环路通过不断调整载波NCO的频率控制字来保持对接收信号载波频率和相位的跟踪。载波NCO要有足够的频率分辨率,保证能高精度跟踪载波,这就要求载波NCO要有足够的相位累加器字长。本设计中累加字长取为32位,累加时钟为60MHz,要求输出频率为50MHz,可以得到频率控制字为:

频率分辨率为: 即通过输入频率控制字来改变输出正/余弦信号的频率时,可以达到0.014Hz的最小步进。另外,也可以根据实际需要的频率改变输入频率控制字值。

即通过输入频率控制字来改变输出正/余弦信号的频率时,可以达到0.014Hz的最小步进。另外,也可以根据实际需要的频率改变输入频率控制字值。

首先在Matlab中仿真一个周期的正余弦波形,由于取8位输出,所以一个周期应该取28个点,均匀取256个点作为一个周期数据。在FPGA中调用ROM单元,存储这256个点值,作为查找表。根据图1的结构原理在FPGA中设计顶层框图如图3所示。图中,sin_rom和cos_rom为正余弦查找表。频率控制字输入在累加器中累加,取累加结果的高8位作为查询地址,在工程中调用sin_rom和cos_rom模块,得到正余弦输出信号。在FPGA中对设计进行仿真,仿真输入控制字为20000000。下载到FPGA中可得到SignalTap II测试结果。仿真和测试结果(图略)验证了设计的正确性。

低通滤波器

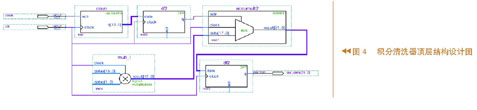

数字低通滤波器实际上是由累加器和寄存器所组成的一个积分清洗器,它的作用是去掉数字混频器后的高次谐波。累加器对数字混频后输入信号与本地码相乘的每一位结果进行累加,经过一个码周期时间(本方案为15000次)的积分累积后,得到一个数据位的相关值。该积分清洗器的累加时钟为中频采样时钟,清洗脉冲是累加一个数据位的进位脉冲,并要求它的时钟沿跟其采样时钟保持一致,其FPGA实现顶层原理结构如图4所示。

在FPGA中对积分清洗模块进行仿真,仿真中输入信号data为1,在某一时刻,使累加清洗信号aclr有效。下载到FPGA中利用SignalTap II对积分清洗模块进行测试,测试中输入数据为1,当累加到14时,使清洗信号有效。测试结果(图略)验证了设计的正确性。

数字鉴相器的设计

科斯塔斯环常用的鉴相器是正弦和反正切鉴相器。对于本文设计的接收机,积分时间T_{d}=0.25ms,4kHz的信号在0.25ms内将变化1周,二象限反正切算法的鉴相范围为[π/2,π/2],因此必须保证输入信号在0.25ms内变化不超过 ,即允许最大的频差为2kHz,否则将得到错误的输出。因此必须对鉴相器的输出进行校正。实际设计时通过计算前后两次鉴别器的输出差值,根据差值大小进行校正,校正算法为:当 ,就对取反,否则 保持不变,其中 为上一次鉴别器误差输出, 为本次鉴别器误差输出。

环路数字滤波器参数的设计

环路选用的是理想二阶环,带宽的大小又决定了整个锁相环的锁定时间和跟踪精度。为了减小噪声引起的相位抖动,提纯输入信号,环路带宽应尽量取窄一些,选取环路噪声带宽跟信息数据速率的比为,其中B_{L}为环路噪声等效带宽,R_{b}为信息数据速率,一般选取 ,另一方面,也要兼顾捕获时间,从而环路带宽又要求取宽一些,因此应折衷考虑设计的环路带宽。当环路处于频率牵引状态时,要求环路有较宽的捕捉频带,使之能迅速同步频偏较大的载波;当环路处于相位跟踪或锁定状态时,却要求它具有尽量窄的捕捉频带,以保证恢复出的载波相位不产生大的抖动。设计时应根据具体要求来选择环路参数。

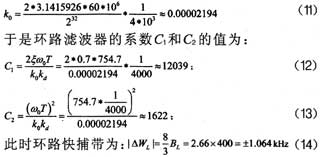

在本方案中,设计要求数据率为4kbps,在频率跟踪阶段,取B_{L}=0.1R_{b}=400H_{z},取ξ=0.7,ω_{0}=B_{L}/0.53≈754.7(rad/s),由于采用反正切的鉴别器算法,所以鉴别器的增益k_{d}可取为1,而NCO的控制灵敏度为k_{0}=2πTf_{s}/2^{N},其中,NCO相位累加器的位数设计中N为32,f_{s}为NCO的采样频率,系统中f_{s}为系统时钟60MHz,即为清洗脉冲的周期1/4k秒。从而得到

在用这组值完成频率跟踪后,取窄带的环路滤波器进行相位锁定。这时取B_{L}=0.01R_{b}=40H_{z},此时的计算结果为:C_{1}=1203.9;C_{2}=16.22;快捕带为:106.4Hz。

总的来说,环路滤波器系数C_{1}和C_{2}需要根据环路的特性选取,它们值的选取是整个环路跟踪性能的关键。 C_{1}主要决定了环路捕捉带的大小,C_{2}则决定了环路的长期跟踪速度和环路捕获速度。C_{2}较大时,环路将经过相当长的时间才能成功入锁。若用一个固定的环路滤波器,由于锁定时间和精度的不同要求,捕捉时间远小于跟踪时间,这样得到的结果显然不是最优的。为了使环路既具有快速捕获的能力,又能在跟踪状态时仅在平衡点附近有细微摆动,使输出相位平缓变化,故应使环路和步进具有自适应调整的能力。可以采用环路切换法,即在不同时刻转换环路滤波器的参数。

环路的Matlab仿真

分别利用正弦鉴相器和反正切鉴相器,在Matlab中仿真一个连续波的跟踪过程。生成连续正弦波的频率为10MHz,采样频率为80MHz,初始相位为30 。利用图1的环路电路,通过设置环路滤波器的参数,仿真其跟踪过程,并对跟踪结果分析。

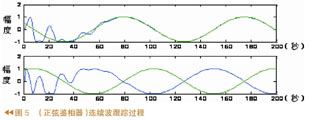

跟踪过程如图5所示。横坐标为时间,纵坐标为信号幅度。图5、6分别是利用正弦鉴相和反正切鉴相后,NCO的同相和正交输出,同相输出即为跟踪结果。对比可知,反正切鉴相时40s就可以实现正确跟踪,而正弦鉴相则要到80s才能实现。

比较正弦和反正切鉴相器的输出(图略),开始时输出误差较大,通过环路的调整,输出误差信号逐渐减小,最终趋于稳定。稳定后的输出最小值是鉴相器的最小分辨率,即为跟踪精度。跟踪精度除了和鉴相器本身特性有关,还和环路滤波器的参数设置有关。通过对比可知,利用正切鉴相器比正弦鉴相器实现跟踪速度快。

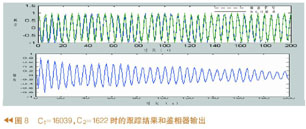

另外对环路滤波器取两组不同参数时环路的性能分别进行了仿真。数字环路滤波器在环路中对输入噪声起抑制作用,并且对环路的校正速度起调节作用。采用理想二阶环,设置C_{1}和C_{2},采用反正切鉴相器,仿真结果如图7、图8。图7是 C_{1}=1200、C_{2}=16时的环路的跟踪结果和鉴相器输出,图8是C_{1}=16039、 C_{2}=1622时环路的跟踪结果和鉴相器输出。横坐标为时间,纵坐标为信号幅度。从图7中可以看出,环路在10s左右即可以实现跟踪,相应的鉴相器的输出也很快维持在0值的附近。如图8,当C_{2}较大时,跟踪时间明显延长,鉴相器的输出波动很大。

环路测试

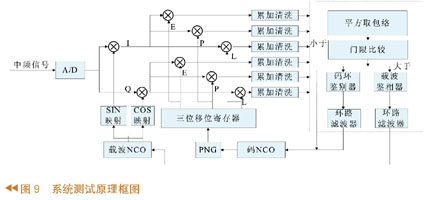

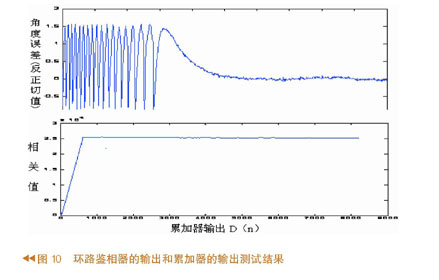

在系统测试中,测试原理如图9所示,在-5dB条件下,载波环带宽为40Hz,码环带宽为10Hz。对载波环路进行测试,载波环鉴相器及累加器的输出如图10所示。在稳定跟踪后,累加器的输出稳定在一个相对固定的数量级上。

结束语

科斯塔斯环由于对载波上的调制信息不敏感,在直扩导航数字接收机中被普遍采用。本环路设计已在一款测距接收机中得到应用,在一片FPGA(EP1C12Q240C8)上编程实现。经测试,在系统可提供33dB的扩频增益的条件下,输入信噪比高于-30dB时,环路正常工作,在-5dB时,多普勒频移±2kHz条件下,经本载波跟踪环路后残余频差小于1Hz,残余相差小于3°。