摘要:为了满足无人机遥控链路远距离、高动态、强抗干扰能力的军事通信需求,设计了基于长码直接序列扩频技术的FPGA实现方案。该方案采用了一种基于FFT算法的快速伪码捕获方法,将传统的伪码相位与多普勒频移二维搜索过程简化为两者同时捕获的一维搜索过程。经过硬件实现与测试,该方案可有效减少硬件资源消耗,同时缩短捕获时间。

关键词:无人机遥控链路;直接序列扩频;长码捕获;FPGA

0 引言

近年来,无人机在军事和民用领域得到了非常广泛的应用。无人机遥控链路是整个无人机系统的神经中枢,可靠性方面要求严格。无人机飞行时复杂多变的环境,特别是远距离巡航时,其低仰角带来的严重多径衰落与高速移动产生的多普勒效应严重影响其遥控链路的可靠性,为了提高其抗干扰能力,保证可靠性,通常采用直接序列扩频技术,并且要求较长的伪码长度。该技术的收发两端要求用完全相同的伪随机码进行扩频和解扩,因此接收机本地参考伪码序列与接收序列之间的精确同步是对接收信号实现解扩的关键,而伪码同步的关键是伪码捕获。

对于1 024位以上的长码扩频系统,传统的伪码捕获方法,捕获时间长,硬件资源消耗大,且动态性能低,不适应于无人机遥控链路。本文采用一种基于FFT算法的快速伪码捕获方法,设计了基于长码直接序列扩频技术的无人机遥控链路FPGA实现方案,经过硬件实现与测试,减少硬件资源消耗的同时缩短捕获时间。

1 遥控链路实现方案

该无人机遥控链路总体技术要求包括:信息速率为14.4 Kb/s;处理增益30 dB;扩频位数1 024位;码片速率22.5 Mb/s;纠错编码采用RS编码;多普勒频移不大于±20 kHz;同步时间小于10 ms;调制方式为QPSK。

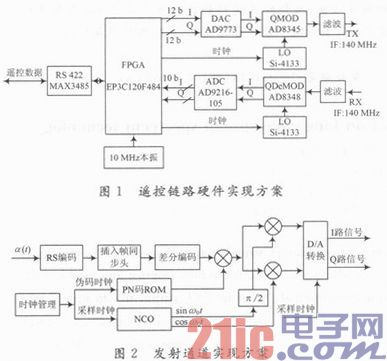

总体硬件实现方案如图1所示。采用收发一体的数字基带处理结构,收发通道在单片FPGA内完成。FPGA选用Altera公司的EP3C120F484,主要的功能都在片内完成,正交下变频解调器选用AD8348,它将中频140 MHz信号正交下变频到基带,形成I/Q两路正交信号,由ADC(AD92 16)完成基带信号的模-数转换,将形成的数字信号传输给FPGA。Si-4133产生中频本振,其工作频率为280 MHz,参考本振为10 MHz。主机接口芯片选用MAX3485,RS 422接口芯片,把解调后的信息传输给主机。其工作时钟频率为波特率的16倍。

1.1 发射通道实现方案

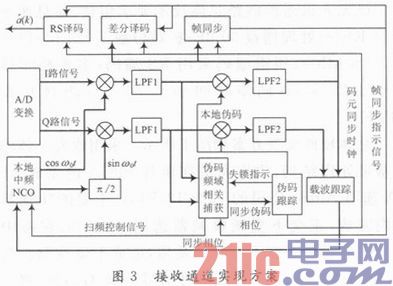

发射通道实现方案如图2所示。遥控指令数据经过RS编码,插入帧同步头,帧同步头采用13位巴克码,然后进行差分编码器,以消除相位模糊问题。随后,对产生的码元序列进行基带扩频,扩频码采用读PN码存储ROM方式产生。FPGA片内集成一个可调NCO,可对扩频后基带数据进行I,Q两路的平衡QPSK调制。调制器输出通过D/A变换送往射频单元。

1.2 接收通道实现方案

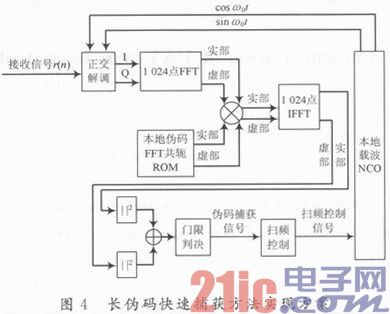

接收通道实现方案如图3所示,对经A/D变换后的I,Q两路数字信号进行解扩解调。解扩采用频域数字相关接收,接收端通过载波同步、PN码同步、帧同步和位同步,严格保证信息正确解扩解调,完成整个扩频通信系统的信息传输。接收通道的关键技术是长伪码的快速捕获。

2 长伪码快速捕获方法

传统的匹配滤波器是在整个码相位和频率域上进行二维搜索,致使需要检测的不确定空间和捕获时间成倍增加。把时域的循环卷积转化到频域,利用快速傅里叶变换来计算,将会大幅度缩小运算量,但将时域、频域二维串行扫描变成并行扫描的方法虽减少了捕获时间,但是以提高硬件的复杂度为代价。

为了处理捕获时间和实现复杂度之间的矛盾,本文采用了一种结合频率捕获和伪码捕获相结合的基于FFT算法快速捕获方法。基于FFT的捕获方法在搜索伪码相位的同时,得到载波频率偏移值,将原来的伪码相位、载波频偏的二维搜索过程变成只搜索伪码相位的一维搜索过程,大大减少了高动态环境中伪码的搜索时间。该方法的FPGA实现方案如图4所示。

FFT的并行捕获搜索过程如下:首先经过正交解调,本地载波NCO对准初始频率估计值,将中频信号解调为基带信息,使产生的信号对准一个频率点搜索,启动FFT捕获环路,做1024点FFT变换,将变换结果和存在ROM内的本地伪码的FFT共轭相乘,再做IFFT,通过比较所有的相关峰值,找出其最大值,若最大值大于设定的检测门限,则表明信号捕获,给出信号所在位置的码相位和载频,进入信号跟踪阶段。如果最大值小于门限,则表明信号未捕获,通过控制逻辑改变载频频差,重复上述过程。采用该方法要注意如下几点:

(1)伪码并行搜索的过程是对时域和频域同时进行搜索,载频频差搜索步进单元的选取很重要。步进单元选的较小,对弱信号的捕获性能较好,但会增加捕获时间;步进单元选的过大,会使相关峰值降低,特别对于低信噪比的信号,不易捕获到,所以载频频差搜索步进单元的选取需要折衷考虑。

(2)在FFT频域并行捕获的同时,可完成对信号载频的提取,因而它可以取代载波频率捕获电路。

(3)在采用FFT频域并行捕获法时,考虑到FPGA的特点.本地伪码FFT值预先存储于FPGA内的存储单元中,这样做的优点在于,省去了一个FFT模块,从而节省了整个系统资源,提高了系统捕获时间。

(4)扫频控制模块受延时锁相控制,在捕获载频频差搜索和伪码捕获后,在延时锁相环路中将对捕获的伪码进行验证,以防止误捕获。

3 实现与测试结果

FPGA的编程实现采用QuartusⅡ9.0集成软件,调试和仿真工具采用该软件自带的在线逻辑分析仪(signalTapⅡLogic Analyzer),可提供适时、高速的指定信号波形。

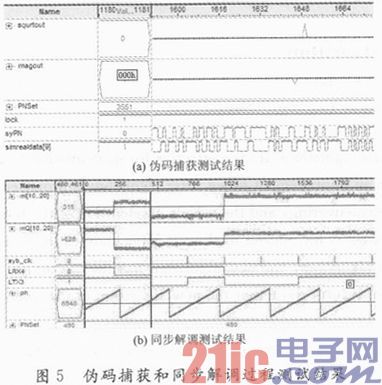

3.1 伪码捕获与同步解调

伪码捕获和同步解调过程的SignalTapⅡ测试结果如图5所示,实验条件为两块实验板之间通过屏蔽线将中频发射和接收端直连,无噪声干扰。

图5(a)为伪码捕获完成,延迟锁定环路还未开始调整伪码时,信号squrtout、imagout波形在相关输出时刻输出了超过门限的相关峰值,PNSet信号表明本地产生伪码和输入信号伪码相位相差3 551个伪码时钟,本地输出的同步伪码序列syPN与输入信号的伪码序列simrealdata的相位相差在一个chip相位内,完成了伪码捕获。

图5(b)中mI、mQ为两路解调输出,syb_clk为同步码元时钟,LRX4,LTX3分别为发射和接收的信息码元,ph为本地NCO的同步跟踪相位,PNSet为本地伪码与发射信号伪码相位差。由图中可以看出mI,mQ已实现同步的解扩解调。ph为一个锯齿波,其斜率是载波的跟踪频偏,它始终跟踪接收信号和本地载波频率的相位偏差,保证本地载波频率和接收信号载波频率及相位保持一致。

3.2 低信噪比条件性能分析

图6为系统高低信噪比条件对比下的SignalTapⅡ仿真图,实验条件为两块实验板之间通过屏蔽线将射频发射和射频接收端连接,射频发射端功率为0 dBm。其中图6(a)信号无衰减,图6(b)加110 dB衰减器。

由图6可以看出,在信号衰减110 dB后,接收到的中频信号ADC_P2B由于信噪比很小(0 dB以下),无法看出发送信号波形,在滤波器输出端F_firoutI信号被噪声淹没。然而,在该扩频系统中,采用1023扩频码,系统理论增益为30 dB,使得信号能正常捕获、跟踪、解调。当然,噪声对系统依然存在很大影响,从图6(b)可以看出,由于噪声影响,载波跟踪环输出的ph信号在锯齿波的基础上,存在不规则抖动,由于系统选取了适合的环路增益,使得这种抖动在系统可接收范围内,从而保证了系统正常工作。

4 结语

本文设计了基于长码直接序列扩频技术的FPGA实现方案,重点阐述了长伪码快速捕获方法的实现,该方法将传统的伪码相位与多普勒频移二维搜索过程简化为两者同时捕获的一维搜索过程。经过硬件实现与测试,系统达到了设计要求,已应用于某型无人机,使用效果良好。