在许多电路设计中,会涉及到可变时钟的问题。比如:一个FPGA和A/D采集芯片组成的采集卡,要求A/D采样时钟可变,FPGA对采样数据进行处理,为保证数据的准确率,首先要对A/D输出的采样时钟进行锁定。

在使用Virtex-5时,简单DCM就无法达到要求,采用动态DC2M就可以解决该问题。另外,在时钟受到干扰的情况下,简单DCM一旦失锁,就无法正常工作,而动态DCM则有能力自回归。

1 DCM的工作原理

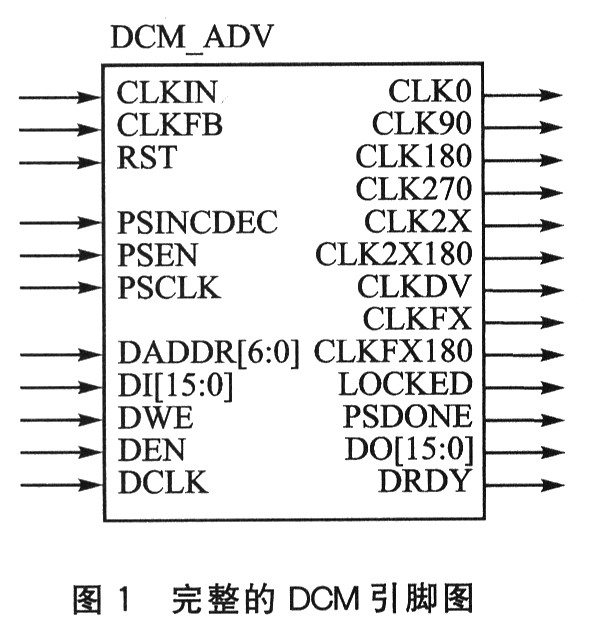

在Virtex-5中,DCM进行升级组合,形成了CMT(Clock Management Technology,时钟管理技术)模块。CMT模块提供了非常灵活的、高性能的时钟,改善了时钟稳定性。每一个CMT模块包含2个DCM(Digital ClockManager,数字时钟管理器)和1个PLL(Phase-LockedLoop,锁相环),这里主要讨论的是DCM的应用。DCM的原型分为DCM_BASE、DCM_PS和DCM_ADV三种,功能依次增强。DCM_BASE只具有基本的时钟矫正、频率综合功能;DCM_PS增加了相位偏移功能;DCM_ADV又增加了动态重配置功能。DCM_ADV的引脚图如图1所示。

1.1 时钟矫正

DCM包含了一个时钟锁定环(DLL),通过矫正输入时钟和输出时钟的时间延迟,用来完全去掉时钟分布延迟。DLL包含延迟单元和控制逻辑。输入时钟驱动一串延迟单元,每个延迟单元的输出代表输入时钟的不同延迟点。控制逻辑包含了一个相位检测器和一个延迟链路选择器。相位检测器比较输入时钟(CLKIN)和反馈时钟(CLKFB),并控制延迟链路选择器,从本质上增加输出时钟(CLKOUT)的延迟,直到CLKIN和CLKFB完全吻合。

1.2 频率综合

DCM提供了2种双倍频频率(即CLK2X和CLK2X180)的独立输出,以及1个对输入时钟固定分频比的时钟输出(CLKDV);另外,还提供了一个对输入时钟分频加倍频的复合时钟输出。用户可以定义任意的(固定范围内)倍频比M和分频比D。如果数值计算上存在可能,内部的计算器会自动做出适当的选择让输出时钟边沿和输入时钟相吻合。比如,若M=9并且D=5,则复合频率输出是输入时钟的1.8倍,并且每5个输入周期或者每9个输出周期时间,输出上升沿与输入上升沿同步一次。

1.3 相位偏移

DCM有2种相移:一种是固定粗调相移,另一种是细调相移。固定粗调相移包括90°、180°、270°。相对于CLKO,分别产生了CLK90、CLK180、CLK270时钟输出;相对于CLK2X和CLKFX,则只产生了CLK2X180和CLKFX180时钟输出。细调相移又分为4种模式:固定的,正相可变的,中心可变的和直接模式。细调相移是在粗调的基础上进行的。在固定模式下,就是要配置一个固定的相移量,并且相移量要是1/256时钟的整数倍。在正相可变和中心可变的模式下,相位可以动态重复地向前或者向后移动,移动步长是时钟的1/256。在直接模式下,根据DCM_TAP的数值,相位能够动态地、相对地向前或者向后移动。

1.4 动态重配置

通过一组数据总线,在不改变其他设备的情况下,改变DCM的属性。用于动态重配置DCM功能的引脚有:输入引脚DADDR[6:0],DI[15:0],DWE,DEN和DCLK;输出引脚DO[15:0]和DRDY。动态重配置可以实现DCM的不同相移,根据目前的配置设定,可以改变乘数(M)和分数(D)。

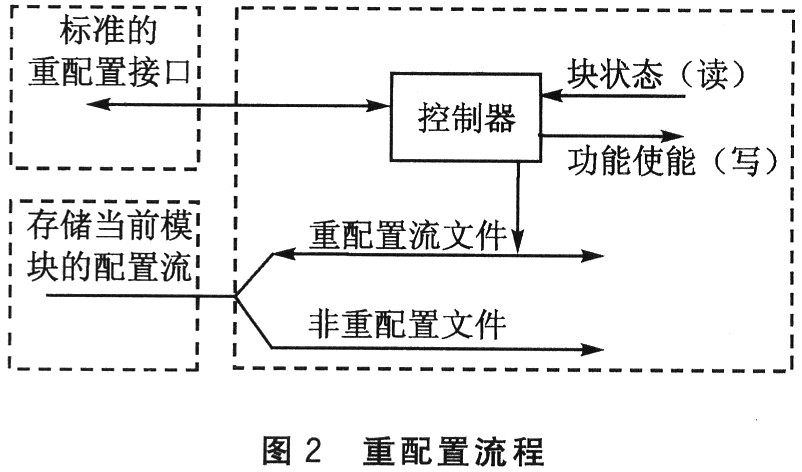

DCM的动态重配置功能是通过动态重配置引脚(Dynamic Reconfiguration Ports,DRP)完成的,不仅可以配置DCM,而且可以配置FPGA的其他逻辑。动态重配置逻辑块的重配置流程如图2所示。

对于Virtex-5的DCM,乘数(M)和除数(D)的值是通过DRP往地址50h写数来实现的。M的值放在16位DRP控制字的高8位,D的值放在低8位。在写控制字的过程中,DCM必须保持Reset状态。地址41h的位3(DI[2])是用来设置DFS的频率模式的,0是低频工作模式,1是高频工作模式;地址51h的位3和位4(DI[3:2])是用来设置DFS的频率模式的,00是低频模式,11是高频模式;地址00h用来存储DCM的默认输出状态。

2 动态DCM的原理和设计

动态DCM是在DCM特性的基础上进行的应用设计。大致可以分为2种:一种是在DCM_BS和DCM_PS基础上设计的,带有反馈回路的DCM;另一种是在DCM_ADV基础上设计的,反馈回路和重配置接口相配合的设计应用。

2.1 反馈回路的设计

带反馈回路的动态DCM,主要是针对DCM_BS和DCM_PS设计的。由于这两种DCM不具有可重配置功能,因此在输入时钟变化范围超过了最大允许变化范围时,必须进行手动复位。如果能够在重配置功能上引入一个反馈回路,就可以极大地提高DCM的动态频率范围,并可以实现DCM的失锁自启动。

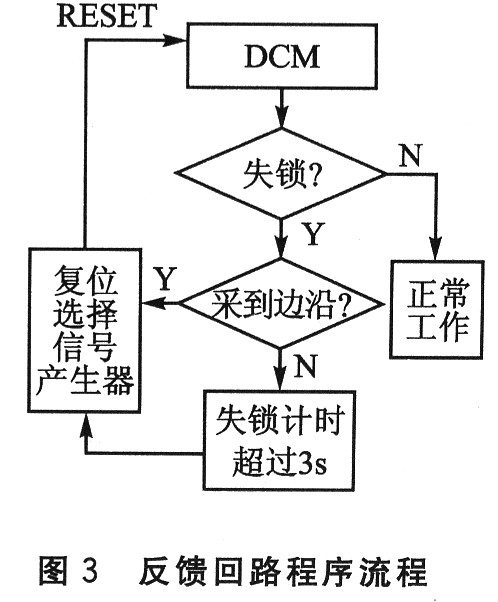

反馈回路的工作过程是:对DCM的失锁信号进行处理,然后反馈给DCM,让DCM重新锁定。失锁信号的处理过程分两个方面同时进行:一方面,采用FPGA的其他稳定时钟源对失锁新号采边沿,然后把边沿信号整形为复位信号所要求的脉冲波形,延时一定的周期后,送到DCM的复位端,对DCM进行复位。另一方面,对失锁信号用稳定的时钟源进行计时,计时超过3 s(可以根据应用修改计时时间),如果失锁信号一直有效,就产生一个脉冲,对DCM进行复位,循环往复,直到DCM正常工作。程序流程如图3所示。

反馈回路的原理分析:当DCM输入频率变化超出了允许的范围后,DCM开始失锁,此时通过稳定的时钟源采集DCM的失锁信号;然后对DCM进行复位,由于DCM中含有时钟锁定环路(DLL),DLL会对新的时钟产生一串延迟单元,形成延迟链路。DLL中的相位检测器比较输入时钟(CLKIN)和反馈时钟(CLKFB),并控制延迟链路选择器,选择合适的时钟输出,直到CLKIN与CLKFB完全吻合,完成新一轮的锁定。如果在时钟锁定的过程中,输入时钟再次发生变化,将会导致DCM无法锁定。此时,启动第二个进程,对失锁信号进行计时,超过额定时间,就对DCM进行复位,直到DCM正常工作。

由整个分析过程可以看出,通过增加反馈电路后,DCM可以适应不同输入时钟的变化。但是输人时钟并不是无限可变的,DCM有高频和低频的区别,高频的DCM无法适应低频的输入频率,同样低频的DCM也无法适应高频的输入时钟。因此,在IP核生成时,就决定了输入频率的变化范围,这个范围可以在IP核生成时的数据手册中查到。

2.2 反馈回路与重配置接口的配合

就DCM_ADV而言,由于其具有可重配置功能,所以它本身就提供了强大的动态频率变化范围;并且在配置中可以选择DCM的高频和低频属性,因此它具有更加广泛的频率范围,高、低频都可以适应。不仅如此,可重配置功能还可以动态地改变DCM的相位偏移和复合输出时钟的分频比。但是,重配置功能的使用需要一个外部控制器对FPGA进行配置,硬件结构相对复杂。在不需要控制器的应用场合,它的使用受到限制。

对于可重配置功能,在操作时要注意两点:一是需要动态改变的CLKFX的乘数(M)和除数(D)的值要先减去1,比如希望分频比是9/4,就需要载人M/D=8/3。二是在写入动态控制字时,要保持DCM处于复位状态,直到控制字写完后才释放复位状态。

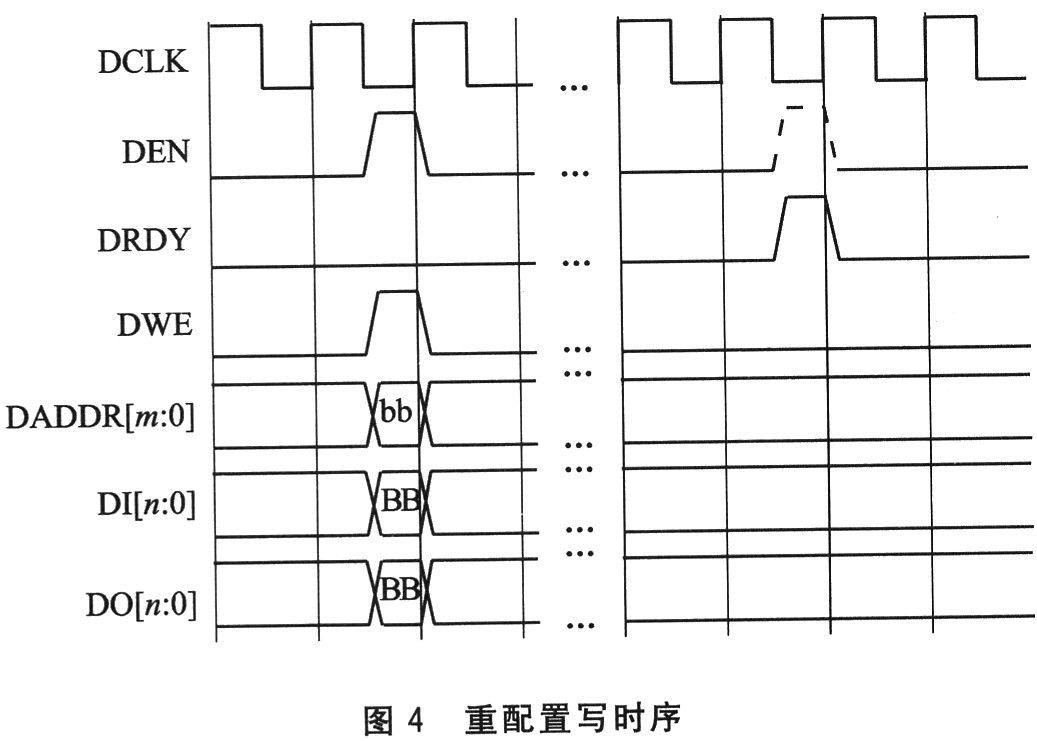

重配置功能的写时序如图4所示。其中,DCLK是其他接口信号的驱动时钟,在上升沿同步工作;DEN是其他接口的使能信号;DWE是读/写控制信号,如果DWE是FALSE,为读操作,否则就是写操作;DADDR是读/写地址总线;DI是数据输入总线,只有当DEN和DWE同时有效时数据有效,而且实际的写操作是在DRDY返回之前的某个时刻发生的;DO是数据输出总线;DRDY是与DEN对应的一个信号,标志着一个DRP操作周期的完成,DO总线数据要在DRDY有效时间内DCLK的上升沿读取才有效。

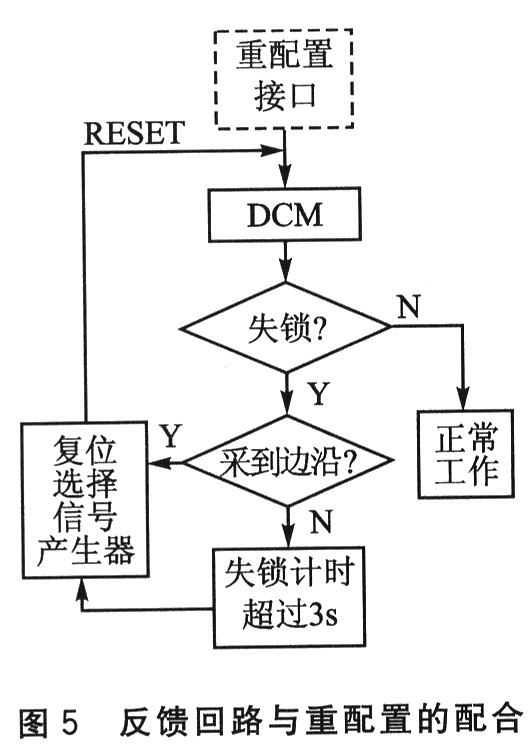

如果可重配置功能与反馈回路相互配合,就能实现功能更加完善、运行更加稳定的自适应DCM。反馈回路主要完成对时钟变化的自适应;而可重配置功能则主要完成高频或者低频DCM的选择,相位偏移的控制以及复合频率(CLKFX)的设置等。两者相互配合,既可以降低只用重配置功能造成的复杂度,提高稳定性,又可以弥补反馈回路无法实现的复杂时钟管理功能。功能框图如图5所示。

结 语

自适应DCM在FPGA电路设计领域有着广泛的应用,本文实现了带反馈回路的多种自适应DCM,并讨论了在设计中遇到的一些关键性问题。仿真结果表明,本文设计的自适应DCM符合系统的设计要求,并在工程实践中取得了很好的效果。