基于FPGA的中频AGC电路设计.pdf

时间:09-01 16:38

查看:2518次

下载:162次

简介:

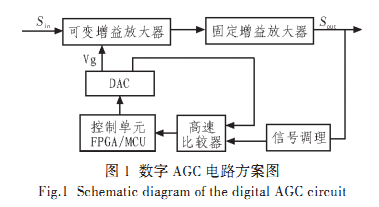

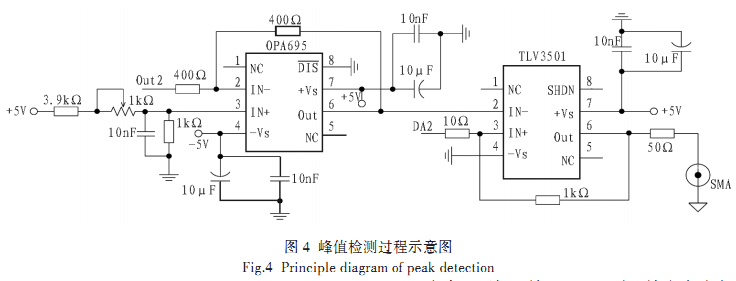

传统数字自动增益控制(AGC)电路采用模数转换器(ADC)采集信号后进行信号处理得到幅值信息实现自动增益控制,此过程对采样速率和算法要求较高。为降低对ADC采样速率和后级信号处理算法要求,设计了一种采用高速比较器与数字器件(DAC+FPGA/CPLD)实现的峰值检测电路,并将其应用在中频数字自动增益控制电路中,电路可以在1 MHz至60 MHz对信号进行自动增益控制,可以将峰峰值稳定在2±0.2 V范围。