基于VHDL的数字频率计的设计-毕业设计

时间:10-29 10:38

查看:898次

下载:162次

简介:

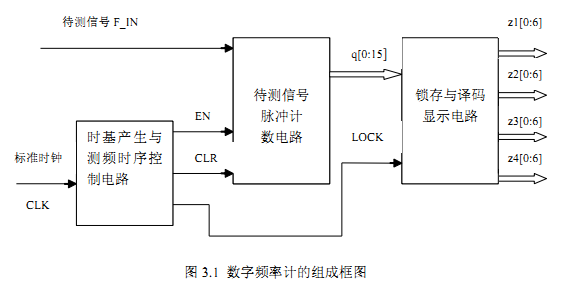

本文介绍了一种自顶向下分层设计多功能数字频率计的设计方法。该频率计采用 VHDL 硬件描述语言编程以MAX+PLUSⅡ为开发环境,极大地减少了硬件资源的占 用。数字频率计模块划分的设计具有相对独立性,可以对模块单独进行设计、调 试和修改,缩短了设计周期。该数字频率计的测量范围为lHz~1MHz,响应时间 小于等于15 秒;其测试结果由4 只七段数码管稳定显示,测量误差小于等于1 % 。仿真波形与分析结果表明,所设计的电路通过硬件仿真能够满足数字频率计的功能要求,具有理论与实践意义,实现了电子电路自动化的过程。数字频率 计模块划分的设计具有相对独立性,可以对模块单独进行设计、调试和修改,缩短了设计周期。