高斯噪声源电路的设计与实现.pdf

时间:12-15 11:43

查看:1424次

下载:162次

简介:

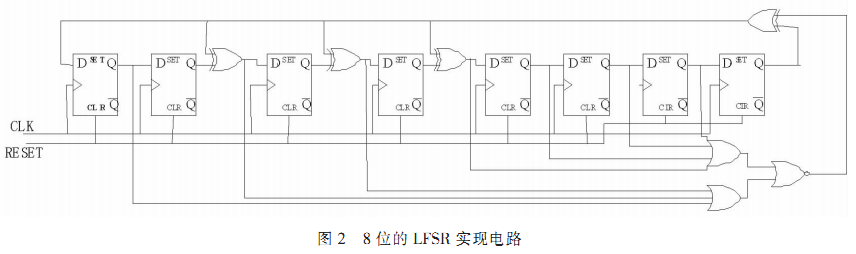

为了实现占用资源少、精度高的高斯噪声源电路,设计了一种新的高斯噪声产生方案,该方案在FPGA上通过线性反馈移位寄存器产生高速均匀分布伪随机数,接着利用均匀分布与高斯分布之间的映射关系生成高斯噪声,并创新地采用非均匀划分的折线逼近映射曲线,同时设计寻址电路,从而减少噪声源占用的资源,改善噪声精度。在XILINX Virtex5 XC5VLX50T上的实现结果表明,该方案仅使用了2%的可配置SLICE和1块片上BRAM,实现了±4σ(σ为标准偏差)的高斯噪声源。时序分析表明其最高频率可达131 MHz。