FIR数字滤波器的FPGA实现研究.pdf

时间:01-09 16:56

查看:1993次

下载:162次

简介:

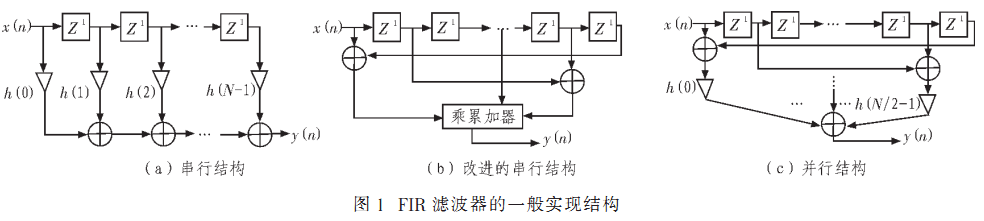

为了研究不同结构的FIR数字滤波器FPGA实现对数字多普勒接收机中FPGA器件资源消耗及其实现的滤波器的速度性能,在Xilinx ISE10.1开发平台中,采用Verilog HDL语言分别实现了FIR数字滤波器的改进的串行结构、并行结构以及DA结构,并在ModelSim仿真验证平台中仿真了实现设计。结果表明,改进串行结构的实现消耗资源少但滤波速度慢,并行结构的实现滤波速度快但消耗资源多,而DA算法的实现速度仅取决于输入数据的宽度,所以滤波速度通常较快且消耗的资源较少。