嵌入式高速数据采集处理模块的设计实现.pdf

时间:03-28 15:21

查看:1139次

下载:163次

简介:

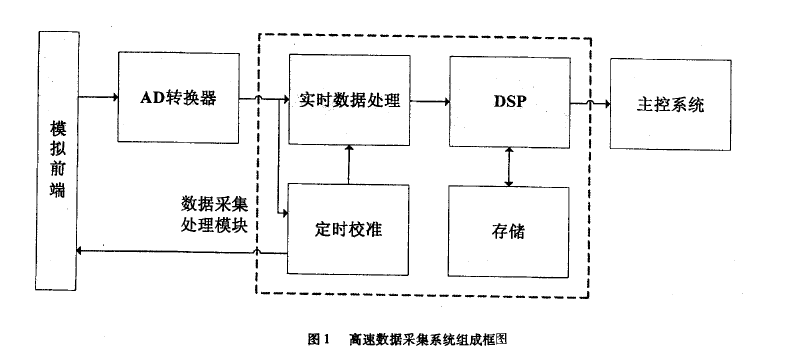

本文主要提出了DSP+FPGA的架构实现嵌入式高速数据采集的思想,以提高采集系统的整体性能。并且将抽取、内插、FFT和多种滤波处理按照特性在DsP与FPGA上进行了相应的优化设计及实现,从而大大提高了处理性能,而且H呵和滤波可并行处理,进一步提高了系统运行速度和效率。该系统还可以通过对FPGA内下栽不同的内容及改变DsP程序来实现在最小改动前提下对系统进行功能扩展、改变及升级,从这个方面讲,这个系统具有一定的灵活性、先进性和前瞻性。