AD转换电路设计

本设计中选用的AD转换芯片是TI公司的TLC320AD50C($25.0250)。该芯片的采样采用ΣΔ技术,即将一个抽样滤波器放置于ADC后,将一个差值滤波器放置在DAC前。这种结构的最大特点就是使系统可同时进行接收、发送任务。TLC320AD50C可实现高采样率(最高可达 22.5kb/s)的AD/DA转换,该功能由2个16位的同步串行转换通道实现,可直接和DSP连接进行通信。TLC320AD50C中的可选项和电路配置可以通过串行口进行编程,该芯片对掉电、复位、信号采样率、串行时钟率、增益控制、通信协议、测试模式等可通过串行口进行编程和电路配置。具体连接如图3:

片外复位电路提供上电复位,晶振电路可提供10MHz的主时钟频率,数据采样频率和其他时钟信号均由此频率分配。5402与AD50C之间的通信格式为主串行通信格式:接收和发送转换信号。存储采集到声音信号后,一个很重要的环节就是声音信号的存储,本系统中我们采用的是SST公司的FLASH存储器:SST39VF400A($0.8875)。该器件存储容量为4MB,采用3.3V单电源供电,对各个子模块的读写和擦除,可通过一些特殊的命令字序列来实现且无需额外提供高电压。在此设计中我们利用DSP编程实现对该存储器的读写操作。DSP主要通过外部存储器接口(EMIF)访问片外存储器。它不仅具有很强的接口能力(可以和各种存储器直接接口),而且具有很高的数据吞吐能力。5402与SST39VF400($0.8875)的接口电路设计如图 1所示。该电路主要通过DSP的相关输出管脚来控制FLASH的擦除和读写。其中,A0~A19为地址线,DQ0~DQ15为数据线,OE和WE分别为输出使能和写使能,CE1为片使能。

声音信号经过AD转换器以后传输给DSP,由DSP的PS和DS引脚通过逻辑开关来分别控制flash和sram的使能端,由DSP的 R\W和MSTRB控制位通过逻辑电路分别控制读和写。在本设计中,SRAM使用的是GS1117:64K&TImes;16的1MB异步静态随机存储器。 GS71116是一个由高速的互补性金属氧化物半导体晶体管(CMOS)组成的静态随机存储器,不需要外部时钟或时间频闪观测器。3.3V的操作电压,所有的输入输出均兼容晶体管逻辑电路(TTL)。它的快速通道时间小于15ns,操作电流小于100mA。

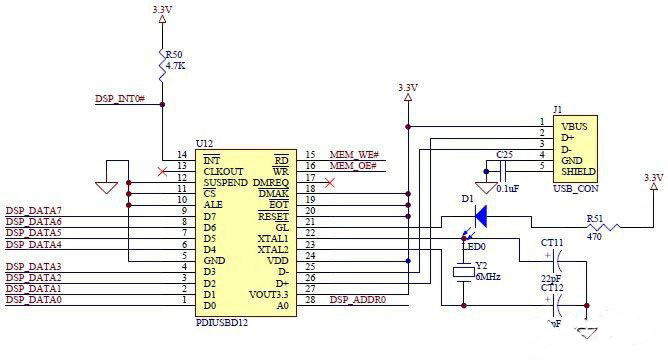

USB接口电路设计

PDIUSBD12是一款带并行总线的USB接口器件,它符合通用串行总线USB1.1版规范,集成了SIE、FIFO、存储器收发器以及电压调整器等,可与任何外部微控制器或微处理器实现高速并行接口2M字节/秒,且在批量模式和同步模式下均可实现1M字节/秒的数据传输速率,可通过软件控制与USB的连接,采用GoodLink技术的连接指示器,在通讯时使LED闪烁,具有可编程的时钟频率输出,内部上电复位和低电压复位电路,为双电源操作,在3.3±0.3V或扩展的5V电源下均可使用,可实现多中断模式的批量和同步传输。连接图如图4:

JTAG接口

JTAG是jointtestactiongroup的简称,是用来调试DSP的仿真部分,其连接部分要和仿真器上的引脚一致。TI公司的 DSP5000系列专门预留有JTAG管脚,共14个,4,8,10,12引脚均接地,6引脚悬空,5接高平电压3.3V,所有的仿真引脚均使用 IEEE1149.1标准,其余的引脚含义为:1、TMS:输入引脚,选择测试方式;2、TRST:输入引脚,测试复位;3、TDI:输入引脚,测试数据输入;7、TDO:输出引脚,在TCK的下降沿时输出数据,其余时间呈高阻态;9、TCK_RET:输入引脚,在板子与仿真器的连接电缆不小于6英寸的时候,接法与TCK相同,大于6英寸的时候,需另加驱动;11、TCK:输入引脚,测试时钟,一般为占空比为50%的固有时钟信号;13、EMU0:仿真中断引脚0,可用作输入或输出;14、EMU1:仿真中断引脚1,可用作输入或输出,当TRST为低电平、EMU0为高电平时,EMU1为低电平,所有输出禁止。