摘要:讨论了电磁干扰传输的一般产生、传播途径及在电子电路系统中进行电磁兼容设计的目的及相关内容,并以美国TI公司TMS320C24x系列芯片为例,阐述了DSP应用系统进行电磁兼容设计的一些常用方法和技巧。

1引言

随着DSP芯片的迅猛发展,其运算速度和处理能力不断提高,使得DSP系统的成本、体积、重量及功耗都有很大程度的下降。但与此同时,周围环境的电磁干扰源越来越多,使得DSP系统和产品设计人员也面临着更加严峻的挑战,即如何抑制日益严重的电磁干扰(EM I) ,提高系统性能,使各种电气及电子设备达到电磁兼容(EMC) 。

2电磁兼容设计

2. 1电磁兼容

电磁兼容(EMC)是指在有限的时间、空间和频谱资源等条件下,各种用电设备可以共存并不至于引起性能降级的一门学科。而电磁兼容性通常是指设备或系统在其电磁环境下能正常工作,并且不对该环境中任何事物构成不能承受的电磁骚扰的能力。

电磁干扰( EM I)是指电磁骚扰引起的设备、传输通道或系统性能的下降。形成电磁干扰必须具备三个要素, 即: 电磁骚扰源、耦合途径和敏感设备。三者关系如图1所示。

图1EM I的三要素。

任何形式的自然现象或装置所发射的电磁能量,使生物受到损伤或使其他设备、系统发生电磁危害,从而导致性能下降或故障,这种自然现象或装置就称为电磁骚扰源。如光照、天电噪声、电子噪声、发电机等都属于电磁骚扰源。

耦合途径是指传输电磁骚扰的媒介或途径。

敏感设备是指当受到电磁干扰时,会受到伤害的生物及会发生电磁危害,导致性能下降或发生故障的器件、设备或系统。许多器件、设备或系统既是敏感设备又是产生干扰的电磁骚扰源。

2. 2电磁兼容设计的目的

电磁兼容性设计的目的:是使电子设备或电子系统在预期的电磁环境中实现电磁兼容。即要求在同一电磁环境中的设备或系统都能正常工作又互不干扰,达到“兼容”的状态。满足电磁兼容( EMC)有以下两方面的规定:

(1)能在预期的电磁环境中正常工作,无性能降低或故障;(2)对该电磁环境来说不是一个干扰源。如果一个DSP系统符合以下条件,则该系统是电磁兼容的。

·对电磁骚扰不敏感。

·对系统自身不产生干扰。

·对其他系统不产生干扰。

为了实现电磁兼容,必须从形成电磁干扰的基本要素出发,从分析电磁骚扰源、耦合途径和敏感设备入手,采取有效的技术措施,抑制骚扰源、减弱或消除骚扰的耦合途径、降低敏感设备对骚扰的响应。

2. 3电磁兼容设计的基本内容

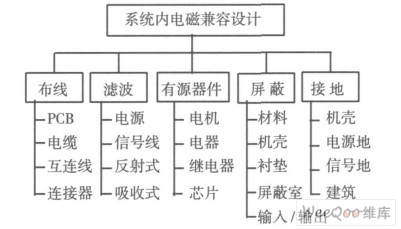

电磁兼容设计可分为系统间和系统内两方面加以考虑。系统间的电磁兼容设计目前已经研究的较多,本文将主要针对系统内的电磁兼容设计加以讨论。

通常系统内电磁兼容设计可分为五部分:有源器件的选择和印制电路板( PCB )的设计、布线、滤波、接地及屏蔽等。如图2所示。

图2系统内EMC设计。

2. 4电磁干扰的传输途径

电磁骚扰源与敏感设备的耦合途径有:传导、感应、辐射或三者的组合。

传导耦合是电磁骚扰源和敏感设备之间的主要耦合途径之一。传导耦合的方式很多,可以通过电源线、信号线、接地导体等进行耦合。防止传导耦合的方法是避免导线感应噪声,采取适当的屏蔽或将导线分离,或在干扰进入敏感电路之前,用滤波的方法将其滤除。

感应耦合是电子元件(例如继电器、变压器、电感器等)及导线之间的主要耦合方式。可分为电感应耦合和磁感应耦合两类。对这两类耦合可以采用加屏蔽、隔离或改变骚扰源和敏感设备的相对位置的方法加以抑制。

辐射是骚扰传输的另一种方式,包括天线、电缆、机壳之间产生的干扰。

通常,一个设备或系统中存在诸多的耦合途径,一般采取抑制骚扰源、减小骚扰源和敏感设备之间的耦合、降低敏感设备对骚扰源的灵敏度来设计系统,达到电磁兼容的要求。

3系统内EMC设计中采取的措施

3. 1有源器件的选择和PCB的设计

在数字电路特别是高速数字电路设计中,有源器件的正确选择和印刷电路板( PCB)设计对防止电磁干扰( EM I)是至关重要的环节。

在器件的选择过程中必须注意有源器件的固有电磁敏感度特性和电磁骚扰发射特性。*价敏感器件的重要参数有灵敏度和带宽,灵敏度越高,带宽越大,抗扰度越差。电子器件的电磁骚扰发射也是应该注意的,应尽量避免或降低对其他器件或系统产生的干扰。

在PCB板设计中,应充分考虑板的结构、器件的布局、线路安排及滤波等技术。以下是一些值得参考的技巧:

·电路中的电流环路应保持最小

·使用较大的地线平面以减小地线阻抗

·信号线和回线应尽可能接近

·电源线和地线应相互接近

·在多层板设计中,电源面和地平面应当分开

·采用合适的布线宽度以增加高频阻抗和降低电容耦合

·数字地、模拟地等应相互分离

·采用多点接地降低高频地阻抗

·增大相邻激励线迹的间距减小串扰

·尽量减小时钟信号环路面积

·高频线路和时钟线要短并尽可能直接连接

·敏感的线路不要与传输高频大电流开关转换信号的线路并行

·不要有浮空数字输入,以防止产生开关误动作和噪声

3. 2滤波技术

在电子系统设计时经常在电路中加入电容器来满足系统工作时所要求的电源平稳和洁净度。

根据电容在电路中的作用可分为:去耦电容、旁路电容和容纳电容。去耦电容用来滤除高速器件在电源板上引起的骚扰电流;旁路电容可用来消除高频辐射噪声,从而抑制共模干扰;容纳电容则配合去耦电容抑制由电流变化引起的噪声。

主要的滤波技术包括:

·对电源线和所有进入PCB的信号进行滤波

·旁路快速开关器件

·旁路模拟电路的所有电源供电和基准电压引脚

·在器件引线处对电源/地去耦

·用多级滤波抑制不同频段的电源噪声

3. 3其它降噪措施

·根据系统功能和实现目标要求可以采用悬浮地、单点接地、多点接地和混合接地等不同的接地方式

·在适当的地方加屏蔽

·对有干扰的引线进行屏蔽或绞在一起以消除相互耦合

·在感性负载上用箝位二极管等

4DSP应用系统的电磁兼容设计

DSP系统具有高精度、小功率、快速逻辑等特点,容易受到寄生阻抗、介质吸收或高频噪声的影响 。在高速数字电路中,特别是在快速DSP中,时钟电路通常是宽带噪声的主要和最大产生源,可产生高达300MHz或更高的的谐波干扰,应采取措施加以克服。此外,系统复位线、中断线和控制线是较容易受到干扰的敏感设备。

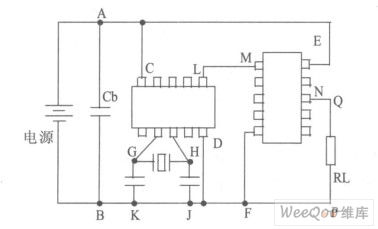

一个电子系统的电磁兼容性很大程度上取决于元件的布局和导线的连接形式。当一段导线和相应的回路中有电流流动时,便产生了天线效应,向外辐射电磁能量,此能量的大小与流过电流的幅值、频率及该电流环路所包围的面积有关。从而形成了一个典型的电磁干扰源。

图3电子系统内部的电流环。

如图3所示,环路A—C—D—B和A—E—F—B中传输着系统正常工作所需的能量。然而电路中所消耗的能量不是恒定不变的,这主要取决于系统中各元件的瞬时工作状态。系统中每个器件动作所引起的变化都将反映到这些传输线上。为了防止电流的快速变化引起的干扰,可借助电容Cb加以抑制。由信号线和控制线形成的回路N—F—P—Q 和L—M—F—D所包围的面积相对较小,但是由它们引起的高频噪声也是不容忽视的。由晶振等元件组成的环路G—H—J—K,通常是系统中信号频率最高的区域,在进行电磁兼容(EMC)设计时应当重点考虑。

由以上分析可见,在DSP应用系统设计时要重点考虑电源线、高频信号线和时钟振荡电路的设计。

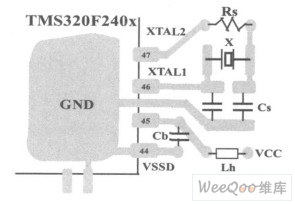

对于电源线来说,可以采用去耦电容和铁氧体保持供电电源的稳定。信号线及其回路组成环路包围的面积越小越好,以减小辐射干扰( EM I) 。在数字系统中时钟信号通常是频率最高的信号。以图4 为例,当晶振连接C24x系列内部振荡器时,通过减小高频电流和电流环路包围的面积来抑制电磁干扰。

晶振具有很高的阻抗(通常为几百千欧) ,因此其工作时产生的高频电流幅值很小。然而CMOS电路的输出是含有高次谐波分量的方波信号,晶振自身对这些信号不具有高阻抗特性,从而将产生较大的谐波电流,可以加一个串联电阻加以抑制。两个旁路电容对振荡器产生的高频信号来讲,呈现出低阻特性,将在Cs—X—Cs之间产生较大的电流。为了减小辐射干扰,在设计时应尽量缩小这个区域的面积。

图中串联电阻阻值在一千欧范围内。

图4一种推荐的PCB设计方法。

5结束语

针对具体的DSP应用系统,应根据所选芯片类型和功能特点进行电磁兼容设计。例如TMS320C24x DSP,它除了配置有高速数字信号处理的结构,还具有单片电机控制的外设功能,是专门为数字电机控制和其他控制应用系统而设计的。当PCB设计完成后,还可以将C24x PWM单元设置为异步、同步或空间矢量PWM模式,进一步降低电磁干扰。增强系统的电磁兼容性。