以Nand flash为存储介质的固态存储系统中,因为Nand flash的固有特性,在多次读写后,储存在flash中的数据将会变得不可靠。所以有必要开发一种能实现数据可靠传输的手段来提高flash和主控芯片之间数据传输的可靠性。文中介绍了ECC码的特点和原理,在FPGA开发环境下实现ECC校验功能。并通过工程实现,在FPGA上实现了该ECC算法。测试结果表明256 Byte数据生成22 bit的ECC校验数据。能够检测1 bit错误和2 bit错误,并能纠正1 bit错误。

1 引言

评价存储器的一个重要指标就是它的可靠性。在一般的数据存储中,几个位的错误可能不是很关键的问题,但是如果发生在某个敏感的数据上,这个小小的故障可能会导致严重的后果。因此,必须采取一些措施来及时检出并纠正出错的数据。目前常用的方法有:奇偶校验、CRC校验、重复码校验等。

ECC校验是在奇偶校验的基础上发展而来的,它将数据块看作一个矩阵,利用矩阵的行、列奇偶信息生成ECC校验码。它能够检测并纠正单比特错误和检测双比特错误,但对双比特以上的错误不能保证检测。它克服了传统奇偶校验只能检出奇数位出错、校验码冗长、不能纠错的局限性。文中在介绍高速大容量固态存储器的硬件结构基础上,详细介绍了ECC校验码的生成规则以及ECC校验流程,并通过FPGA实现了该算法。

2 存储器的硬件结构及介绍

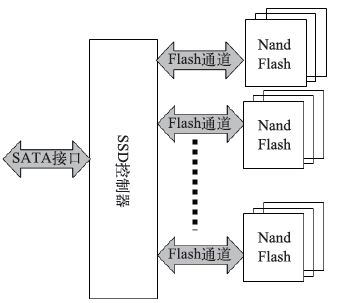

本文中的存储器是以ARM为SSD控制器,用16片Flash芯片构成存储阵列,采用SATA接口实现数据的高速率存储。Flash存储阵列分为8组,每组2片,每组Flash芯片共用数据和控制总线。该存储器的硬件结构如图1所示。

图1 SSD构架图

存储板上的存储芯片用的是Micron公司的高速大容量固态存储芯片Nand Flash Memory,其容量为1 G×8 bit,分为8192个块,每个块又分为64页,1页有(2 k+64)Byte,其中一页有64 bit的空闲区。存储板上的SSD控制器是由ARM 926为核心的控制芯片,它负责数据的缓冲和整个存储器的时序控制,并负责以页为单位生成校验码,并把校验码存入到页的空闲区内。下面以2 048 bit为单位介绍校验码的生成以及校验流程。

3 ECC生成

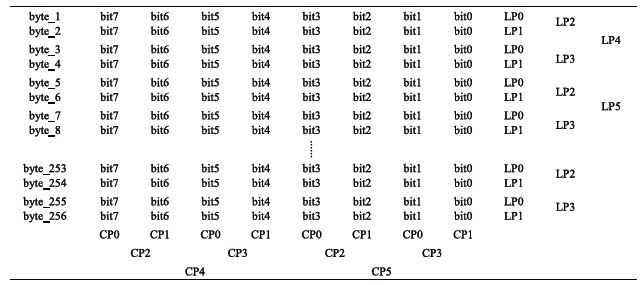

Flash在读写数据的时候是以页为单位进行的,可以以2048bit为单位生成校验码。每个数据有8位信息组成,可以把这2048个数据看成256×8的矩阵,这样就可以分别生成行校验码和列校验码来分别校验。ECC校验中,每256个数据生成3个字节的校验码,这24位的校验码分成3个部分:6位的列校验信息,16位的行校验信息,其余的2位置1,ECC校验码组成,如图2所示。其中CP0、CP1、CP2、CP3、CP4、CP5是列校验码,而LP0、LP1、LP2、LP3、LP4、LP5、LP6、LP7、LP8、LP9、LP10、LP11、LP12、LP13、LP14、LP15是行校验码。行列校验码生成表,如图2所示。

图2 列和行奇偶的框图

处理每个数据字节在整个数据模块上计算列奇偶。

列奇偶位的计算方法为:

CP0=bit7⊕bit5⊕bit3⊕bit1

CP1=bit6⊕bit4⊕bit2⊕bit0

CP2=bit7⊕bit6⊕bit3⊕bit2

CP3=bit5⊕bit4⊕bit1⊕bit0

CP4=bit7⊕bit6⊕bit5⊕bit4

CP5=bit3⊕bit2⊕bit1⊕bit0

其中⊕为异或运算符。

行奇偶位的计算方法为:

LP0=bit7⊕bit6⊕bit5⊕bit4⊕bit3⊕bit2⊕bit1⊕bit0(第1、3、5、7、9……行的总合)

LP1=bit7⊕bit6⊕bit5⊕bit4⊕bit3⊕bit2⊕bit1⊕bit0(第2、4、6、8、10……行的总合)

LP2=bit7⊕bit6⊕bit5⊕bit4⊕bit3⊕bit2⊕bit1⊕bit0(第1、2、5、6、9、10……行的总合)

LP3=bit7⊕bit6⊕bit5⊕bit4⊕bit3⊕bit2⊕bit1⊕bit0(第3、4、7、8……行的总合)

LP4=bit7⊕bit6⊕bit5⊕bit4⊕bit3⊕bit2⊕bit1⊕bit0(第1、2、3、4……行的总合)

LP5=bit7⊕bit6⊕bit5⊕bit4⊕bit3⊕bit2⊕bit1⊕bit0(第5、6、7、8……行的总合)

LP6=bit7⊕bit6⊕bit5⊕bit4⊕bit3⊕bit2⊕bit1⊕bit0(第1到8……行的总合)

LP7=bit7⊕bit6⊕bit5⊕bit4⊕bit3⊕bit2⊕bit1⊕bit0(第9到16……行的总合)

LP8=bit7⊕bit6⊕bit5⊕bit4⊕bit3⊕bit2⊕bit1⊕bit0(第1到16……行的总合)

LP9=bit7⊕bit6⊕bit5⊕bit4⊕bit3⊕bit2⊕bit1⊕bit0(第17到32……行的总合)

LP10=bit7⊕bit6⊕bit5⊕bit4⊕bit3⊕bit2⊕bit1⊕bit0(第1到32……行的总合)

LP11=bit7⊕bit6⊕bit5⊕bit4⊕bit3⊕bit2⊕bit1⊕bit0(第33到64……行的总合)

LP12=bit7⊕bit6⊕bit5⊕bit4⊕bit3⊕bit2⊕bit1⊕bit0(第1到64……行的总合)

LP13=bit7⊕bit6⊕bit5⊕bit4⊕bit3⊕bit2⊕bit1⊕bit0(第65到128……行的总合)

LP14=bit7⊕bit6⊕bit5⊕bit4⊕bit3⊕bit2⊕bit1⊕bit0(上一半行的总合)

LP15=bit7⊕bit6⊕bit5⊕bit4⊕bit3⊕bit2⊕bit1⊕bit0(下一半行的总合)

4 ECC校验

ECC校验可以检测1 bit或2 bit错误,并纠正1 bit错误。

(1)无错误

由于flash中存储的代码和读操作所产生的代码没有不同,因此这种情况下没有错误。

(2)可校准的错误

在计算完所有数据的ECC后和flash中所储存的原来的ECC后产生位比较后,所有奇偶位对(CP0和CP1)…(LP14和LP15)自身有一个错误和一个匹配。这种情况下可以校准错误。

(3)不可校准的错误

在计算完所有数据的ECC后和flash中所储存的原来的ECC后产生位比较后,只要有奇偶对都有错误,如CP0和CP1都有错误这表示多个位错误并不可校准。

(4)可校错误的位置

通过存储在flash中的ECC和从数据中计算出的ECC相异或后,找到错误的位置。(LP15、LP13、LP11、LP9、LP7、LP5、LP3、LP1)这一组数据给出了出错的字节地址。(CP5、CP3、CP1)给出了出错的位的地址。

5 工程实现

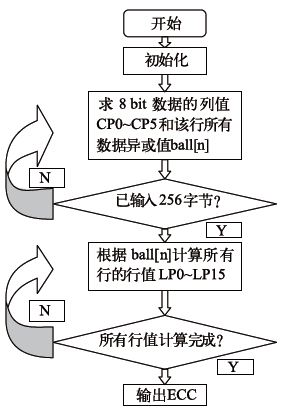

该ECC算法在FPGA中实现,ECC码生成工程实现按照ECC的生成的算法。

算法实现流程图如图3所示。

图3 算法流程

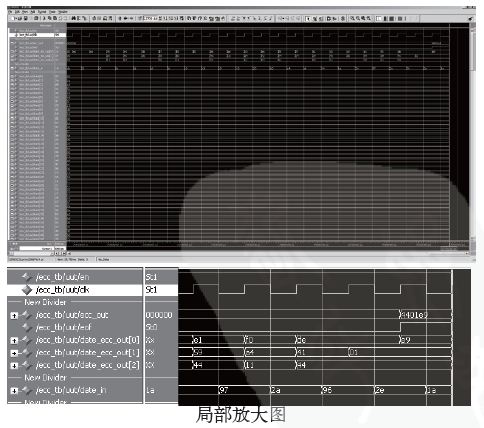

本实验处理对象为256 Byte的数据包,对其进行ECC校验共生成22 bit校验数据。为方便读取,可以在末尾添加两位,形成完整的3 Byte 校验数据。这3 Byte共24 bit,分成两部分:6 bit的比特校验和16 bit的字节校验,多余的2 bit置1,并置于校验码的最低位,在进行异或操作时此2 bit忽略。ECC生成实验结果如图4所示。

图4 ECC计算结果

图4中等待256个字节的数据输入后,最后生成校验码4401E9,也就是3个字节的校验码。其中out1、out2和out3为中间数据,EOF高电平出现代表数据运算结束。运算结束,输出4401E9,其中最后两位为无效数据。数据输入为串行输入,256个字节需要256个时钟周期后才能完成输入。由此从输入开始到得出计算结果至少需等待256个时钟周期。在实际使用过程中可以将串行输入改为并行输入,或流水线结构,以减少等待时间。

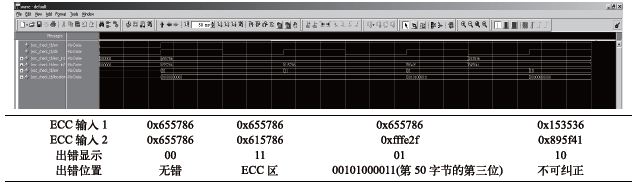

ECC校验的结果如图5所示,其中错误指示由两个bit表示。00表示没有错误,01表示有1位错误,10表示有2位及2位以上错误,11表示ECC区出错。当出错位为1位时,由错误位置指出可纠错的位。

图5 ECC检验

6 结论

为了实现数据的可靠传输,在固态盘中需要使用ECC校验。文中介绍了ECC算法的一种实现方法,说明了ECC的校验流程,最后用xilinxFPGAXC3S500E实现ECC校验算法。ECC校验算法简单,软硬件均能实现,ECC能够检测并纠正单比特错误和检测双比特错误,所以可以为数据存储和通信系统提供一种强有力的差错检测手段。使用本文提供的ECC算法可以纠错1 bit,检错2 bit。