在数字信号处理系统中,大多数高速模数转换器都不能直接与DSP相连接。FIFO恰好架起了DSP与ADC之间的一座桥梁,因为它能缓存大量的数据块。同时由于DSP访问外部存储器器件必须通过外部存储器接口External Memory Interface, EMIF, 而C6000系列DSP的EMIF具有很强的接口能力。它不仅具有很高的数据吞吐率(最高1200MB/s),而且可以与目前几乎所有类型的存储器直接接口。本文介绍了用FIFO 在DSPs和模拟前端(AFEs)之间进行数据缓存的实现方法。

1 AD9042高速模数转换器

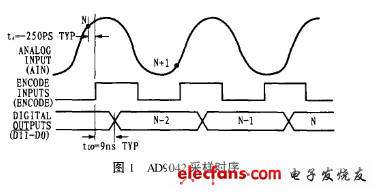

AD9042是一款低功率12bit的41MSPS模数转换器。它的快速、高分辨率特点使其非常适合于视频、多媒体、图像处理、高速数据采集和通信等很多应用领域。图1为AD9042的采样时序图。由该图可以看出:AD9042不能与TMS320C6205直接相连。

因为ADC总是在进行数据输出,因此输出无高阻状态,而如果模数转换器直接与DSP总线相连接,DSP就不能使用其它外围设备了,而且DSP必须在每个转换时钟周期读一次采样数据,这样,即使使用DMA通道传输也是不可能实现的,因为其它外围设备也要使用总线。

虽然采样锁存可以解决数据总是输出的问题,但是,如果模数转换器运行在41MSPS,那么,DSP每24ns就要读一次新采样。这将占去DSP中的大部分I/O带宽,此时如果DSP处于busy态,那么在24ns内就不能读取下一次采样,这样将使数据丢失。

一个比较好的解决办法是使用FIFO作为输入缓冲,由ADC把采样转换的值同步写进FIFO。每写入一块数据便向DSP发出一信号,以提醒DSP从FIFO中读取数据块。这样比单次读的效率要快很多。

2 CY7C4265-10AC同步FIFO

CY7C4265是高速低功耗CMOS时钟FIFO存储器。它是一款同步FIFO,意思是它的读写端口使用同步接口,每一个端口的时钟都是互相独立的,这些时钟可以同步,也可以异步。这使得FIFO的读写口能以不同的速度运行。传统的FIFO在进行数据传输时通常要求额外的控制逻辑,而新一代CY7C4265则可实现FIFO与DSP之间的无缝连接。3 FIFO与EMIF的连接

C6000系列DSP的EMIF具有很强的接口能力,它可以连接不同类型的存储器,如异步SRAM?SDRAM、SBSRAM等。

3 EMIF与FIFO的接口

CY7C4265 FIFOs提供有与DSP的无缝连接,这样的无缝连接要求FIFO作为一个输出缓冲器。而当FIFO作为输入缓冲器时,FIFO是EMIF的唯一异步设备。本设计恰好让FIFO作为输入缓冲器,且就此一个异步设备,因而避免了复杂的接口逻辑。

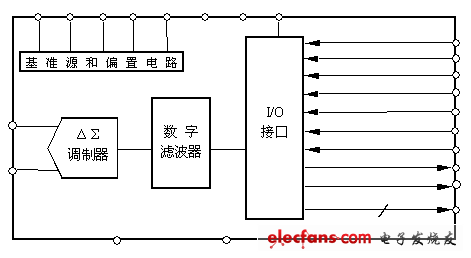

图2是EMIF与FIFO接口的具体硬件实现,FI-FO的半满标志HF作为DSP的输入信号。HF用于告诉DSP此时FIFO中的有效数据是可以读取的(而且容量是FIFO总大小的一半),以便DSP产生一个中断来读取FIFO中的数据块。

3.1 DSP读FIFO时序

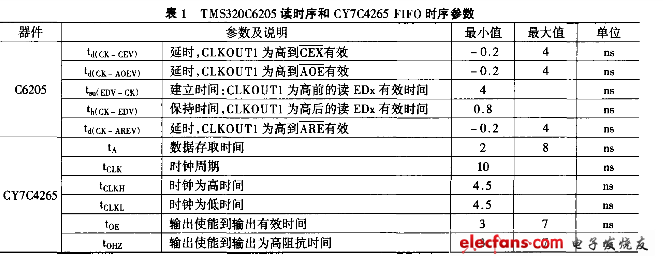

在这个高速微弱信号数据采集卡的设计中,C6205的时钟频率为200MHz,且没有使用其它外部控制逻辑。图2中,EMIF异步接口提供的控制信号可以通过不同的组合(并非都需要)实现与不同类型器件的无缝接口。EMIF的CExCTL寄存器负责设置异步读/写操作的接口时序,以满足对不同速度异步器件的存取要求。

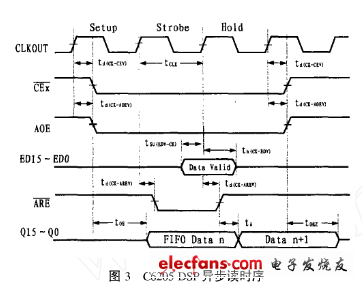

C6000异步接口时序具有很强的可编程性,每个读/写周期由三个阶段构成:建立时间(Setup)、触发时间(Strobe)、保持时间(Hold)。其中建立时间是从存储器访问周期开始(片选?地址有效)到读/写选通有效之前的时间;触发时间是读/写选通信号从有效到无效之间的时间;保持时间则是从读/写无效到访问周期结束之间时间。

DSP的ARE信号作为FIFO的读时钟,FIFO在ARE的上升沿在总线上输出数据,DSP和FIFO的独立时序参数值。

根据DSP的异步读时序,为了完成C6205的建立时间,第一个数据的读取必须满足下式:

Setup+Strobe ≥td?CK-AOEV?max+tOEmax+tSU?EDV-CK?min

根据上式,在最差情况下,建立和触发时间必须大于15ns(4ns+7ns+4ns)。当DSP的时钟频率为200MHz时,一个时钟周期应该是5ns。此时如果Setup和Strobe的值都取1,则Setup+strobe为10ns,故不能满足时序要求,因此Setup和Strobe这两个可编程参数若一个取1,另外一个必须大于等于2。而实际上,Setup和Strobe可以都取1,其原因是C6205不论是连续存取还是单次存取操作,在存取第一个数时,EMIF会自动将最小建立时间设置为2。

而对于以后数据的读取,OE总是有效。现在主要考虑的是FIFO的访问时间应满足下式:

Hold+Setup+Strobe ≥tAmax+tSU?EDV-CK?min

也就是说,一个完整的数据访问时间必须大于12ns(8ns+4ns),即Hold+Setup+Strobe ≥3;要完成C6205的保持时间,必须满足下面两个公式:

td?CK-AREV?min+tAmin ≥ th?CK-EDV?min

Hold ≥th?CK-EDV?min-td?CK-AREV?min-tOHZmin

当上边的式子满足条件时,-0.2+2>0.8。为了得到最小的Hold时间,此时Hold可以为0ns,也就是说,Hold可以被编程为0。

最后要满足的条件是时钟的高低时间。因为FIFO的时钟信号直接由ARE产生,因此ARE信号保持低电平的时间必须大于FIFO的时钟周期。即:

Strobe ≥tCLKL min

Hold+Setup ≥tCLKH min

Setup+Strobe+Hold ≥tCLK min

由以上七个式子可知,在200MHz的钟频率下,CExCTL寄存器中Setup/Strobe/Hold的值可以作如下设置:

Setup=1,Strobe=1,Hold=1;

此时,DSP读取FIFO中数据的速度为66.7MHz。

4 结论

FIFO在ADC高速模数转换器与DSP的通讯过程中起到了很好的数据缓冲作用,其标志位可被用来控制FIFO中数据的读取。如果选用内部时钟频率为133MHz的SN74V2×5-7系列FIFO,DSP读取数据的速度可以达到100MHz。