1 引言

在目前正进行的北京正负电子对撞机二期升级改造工程(BECPII) 中,北京谱仪(BESIII) 的飞行时间(Time of Flight ,简称:TOF) 读出电子学需要对一种具有25ps 分辨率的数据驱动型时间测量器件- HPTDC(High Performance TDC) 进行性能测试。为此,我们设计了一种具有更高精度的专用高精度信号发生器。由于时钟电路是整个高速数字电路的核心部分,时钟信号的质量直接影响整个数字电路逻辑的正确性以及整个电路的性能,因此,对信号发生器的时钟电路进行了大量的PCB 仿真,来研究高速时钟电路的设计,追求对于时钟电路设计的最佳方案。

2 仿真工具的选择

随着电子线路设计复杂程度的增加,以及人们对于电路性能要求的不断提高,越来越需要一定的工具对设计进行验证和性能仿真。Candence 公司提供了一整套完整的电子线路仿真软件,包括VHDL 仿真、原理图仿真、PCB 仿真等等,对于电子工程师进行电路设计是十分有帮助的。这里,利用Candence 提供的强大的PCB 仿真工具SigNoise 来对高速时钟电路设计进行研究。

利用SigNoise 可以对PCB 设计的信号完整性(Signal integrity) 、电磁兼容性( Electro Magnetic Compatibility) 进行分析,帮助电子设计工程师分析电路的信号传输延迟(Delay) 、噪声容限(Noise Margin) 、串扰(Cross talk) 、电磁兼容性等等,及时修改PCB 设计,以获得最理想的信号完整性和电磁兼容性。

3 仿真模型的建立

SigNoise 是建立在DML 模型上的一种PCB 仿真工具。DML 模型是一种SigNoise 可以识别的含有芯片输入输出信息的模型,可以通过IBIS、QUAD 模型转化而成。而Candence 本身提供了模型转换工具Model integrity ,可以在DML、IBIS、QUAD、SPICE 模型之间进行转换,只要我们获得上面的一种模型,就可以方便地得到仿真中需要使用的DML 模型。

在这里,首选IBIS 模型。虽然, IBIS 模型不像SPICE 模型那样含有芯片的内部信息,但是该模型是目前大多数芯片供应商所普遍提供的,可以方便的从供应商的网站上获得,而其他模型却并不是可以容易获得的。同时, IBIS 模型含有芯片输入输出性能的所有信息,完全满足PCB 仿真的需要。

4 仿真电路的建立

对于时钟信号达到几百MHz 的高速电路,时钟信号的传输一般采用ECL 逻辑电平,并通过ECL 器件、无源器件和差分线进行传输,所以本文中以信号发生器设计中使用的Motorola 公司的ECLinPS 系列芯片MC100LVEP111 (1:10 差分时钟驱动器) 和MC100EP131(4 通道的D 触发器) 为例来研究高速时钟电路的设计。

仿真电路由MC100LVEP111、MC100EP131 以及一些匹配电阻组成。MC100LVEP111 将时钟源提供的200MHz 系统时钟进行1 :10 分配,驱动多个MC100EP131。PCB 上的差分线阻抗控制在100 欧。

5 时钟传输的仿真

1) 输线的长度对于高速时钟信号的影响

如图1 所示,MC100LVEP111 提供200MHz 的时钟信号作为MC100EP131 的4 个通道D 触发器的公用时钟, 改变MC100LVEP111 与MC100EP131 之间传输线的长度,对于不同的情况进行仿真,研究传输线的长度对于高速时钟信号传输的影响。

图1 时钟信号传输PCB图

图2 时钟传输电路DML 拓扑图

在SigNoise 中,可以得到以上电路的拓扑图(图2) ,拓扑图含有芯片的IBIS 模型信息、传输线的长度和阻抗信息、匹配电阻的位置和阻值大小信息,可以对信号传输进行十分接近实际PCB 情况的模拟。该电路的仿真结果如图3 所示。

图3 时钟传输仿真波形

表1 中正向过冲(overshoot) 和负向过冲(undershoot) 的定义见图4。

图4 正向、负向过冲的定义

从表1 的数据可以明显的看出,传输线的长度对于高速时钟信号有很大的影响。传输线长度增加,信号的上冲、下冲都显著增加,传输延迟更是大大增加,信号的幅度也有一定的损失。由于时钟信号的频率很高,较大的传输延迟容易导致时序上的错误,从而导致整个电路逻辑的错误。因此,在进行高速时钟电路PCB 设计的时候,要尽可能的缩短时钟信号的PCB 布线长度,以保证信号的完整性和整个电路的时序。

另外,对于要保证时钟同步的高速数字电路,时钟信号PCB 布线的长度更要严格控制,以免由于传输延迟造成各个时钟之间的相位差。在信号发生器时钟电路设计中,使用1 :N 时钟驱动芯片MC100LVEP111 为多个芯片( 例如MC100EP131) 提供同步时钟,需要将每个芯片接收到的时钟信号相位差控制在时钟周期的1 %以内,即相位差要小于50ps。MC100LVEP111 的各个输出时钟信号之间具有25ps 的相位差,所以在PCB 设计的时候,要保证各个时钟线的长度差造成延迟小于25ps。根据仿真结果,要求各个时钟线的长度差要小于166mils。由于各个芯片在板上的位置距离MC100LVEP111 各不相同,为了控制时钟布线长度,使用布“蛇形线”的方式,如图5 所示。在使用这种方式的情况下,设计的信号发生器时钟电路中各个时钟布线长度差最大为50mils。

2) 传输线形状对于高速时钟信号的影响

对于图5 所示的“蛇形”布线方式“, 蛇形”线的间距S ,以及耦合长度Lp ,对于信号完整性有一定的影响,这可以从表2 的仿真结果得到说明。

根据以上的仿真,看到, “蛇形”线的间距越小、耦合长度越大,传输线上信号自身的串扰越大,导致信号具有较大的过冲。因此,为了保证信号完整性,在进行“蛇形”布线的时候,只要PCB 空间允许,应该尽可能的增加布线间距,同时减小耦合长度。根据仿真结果,当S > 4H(H 表示信号线距离参考地平面的高度) 时,这种“蛇形”布线带来的信号串扰可以忽略。

另外,这种“蛇形”布线方式会给信号的传输延迟时间带来影响。图6 显示了在不同的布线方式下,信号的前沿到达传输线终端的时刻,所有这些时刻都是在差分信号的幅度半高宽处测得的。从这张局部放大图,可以看到,“蛇形”布线方式时信号前沿比非“蛇形”布线方式时的信号前沿到达的早,同时“, 蛇形”线的间距越小,这个现象越明显。这是由于在“蛇形”布线方式下,由于并行的距离较近的PCB 连线之间的串扰的影响,一部分信号会垂直的传输到接收端(如图7) ,导致信号的传输延迟时间比不采用“蛇形”布线的时候小。“蛇形”线的间距越小,信号之间耦合越紧密,串扰越大,对信号的传输时间影响也越大。

图6 “蛇形”布线对信号传输时间的影响

图7 “蛇形”布线的信号传输

3) 匹配方式对于高速时钟信号的影响

对于ECLinPS 系列的芯片,信号的上升和下降时间非常短,根据传输线理论,不加匹配所允许的最大传输长度为Lmax ≤tr/ 2td ,约7. 4mm ,所以对于这类高速电路,不加匹配是不可能的,否则就会由于反射导致时钟信号完整性无法保证。由于ECL 电路为射极输出电路,下拉电阻也是必不可少的。在PCB 上,下拉、匹配电阻的合理设置对于信号的质量也有很大的影响。下面就对常见的各种匹配方案进行具体的分析。

第一种匹配方式是最常见的标准匹配,即在信号的始端使用两个510 欧的电阻作为下拉电阻,在信号终端用一个100 欧的电阻跨接在两个差分线上。根据下拉、匹配电阻的位置,又可分为以下3 种情况:

1) 如图1 所示。信号线通过始端510 欧下拉电阻的焊盘,终端也是如此。这样,可以避免由于下拉、匹配电阻的接入而引起的信号线分叉。

2) 如图8 所示。由于匹配电阻要放置在信号线的最末端,才能达到对整段传输线的匹配。所以,在信号线的末端打过孔,将匹配电阻放置在PCB 的另一个元件面,这样,匹配电阻就可以位于信号线的最末端了。

图8 下拉、匹配电阻PCB布局情况2

3) 如图9 所示。有时候,由于PCB 布局紧张,下拉电阻无法与器件放置在同一元件面,这时,可以在信号线上打一个过孔,将下拉电阻放置在PCB 的另一面。

图9 下拉、匹配电阻PCB布局情况3

第二种匹配方式称为并联匹配,电阻放置在信号线的终端,兼作下拉和匹配。这种方式也可以分为两种情况:

1) 如图10 所示。将50 欧的电阻放置在信号线的末端,接到VTT电源上。

图10 下拉、匹配电阻PCB布局情况4

2) 如图11 所示。这种匹配方式称为戴维宁匹配,是上一种匹配方式的演变。在信号线的末端对差分线中的每一根分别加50 欧的匹配,上拉电阻130 欧,接到电源上,下拉电阻80 欧,接到地。

图11 下拉、匹配电阻PCB布局情况5

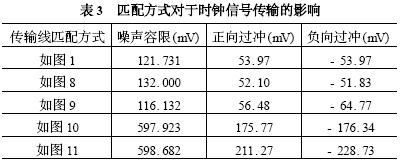

对于以上电路的仿真结果如表3 所示。

(在表3 的仿真中,除了匹配电阻以外,电路的其他部分参数,如信号线长度完全相同。)

比较以上几种下拉、匹配电阻的设计,可以看到:对于标准匹配方式,图8 所示的方法为最佳方案,但是若由于PCB 布局所限,不能采用这种方案,也可以用图1、9 的方式来代替,但是要以损失噪声容限,增大信号过冲为代价。对于并联匹配方式,电路的噪声容限较大,可以避免噪声干扰而引起的误触发,如果电路的噪声可能会很大,最好使用这种匹配方式。然而,在这种方式下,信号的过冲也很大。对比图10、11 的匹配方式,图10 这种方式使用的电阻较少,而且过冲也较小,在性能方面要好于图11 的戴维宁匹配。但是,这种方案使用了一个额外的VTT电源,增加了电路中电源设计的复杂度。同时,这种匹配方式的功耗也很大,对于ECL 电路来说,功耗一直是一个很大的问题,因此这种方案的运用要根据实际电路的功耗要求以及电路中能够提供的电源而定。对于戴维宁匹配,则会导致在信号线终端聚集了大量的电阻,对于PCB 上器件的布局和其他布线带来了一定的困难。因此,对于以上匹配方式的选择,要根据实际情况具体分析。

在信号发生器的实际设计中,为了追求信号完整性,同时考虑PCB 布局空间的限制,使用了如图1、图9、图10 所示匹配方式。根据仿真(如图3 所示) ,以及实际的测试结果,可以看到,即使在使用了匹配的情况下,还是会存在反射现象。这主要是由于各种匹配方式还不能够达到完全的匹配。对于图1、9、10、11 所示的匹配方式,由于PCB 布局的限制,终端的匹配电阻与芯片的管脚之间还是存在一定的PCB 引线,这就导致匹配并不是对整个传输线的完全匹配,带来了一定的反射。对于图8 所示的匹配方式,虽然不存在上述问题,但是在这种方式下,芯片管脚处阻抗的不连续性,也会带来一定的反射。另外,由于电阻在高频情况下,寄生电容和电感的效应会逐渐明显,导致阻抗有较大的改变,使实际的信号含有一定的反射。

6 结论

通过SigNoise 的PCB 仿真结果,可以看到,设计高速时钟电路的时候,由于电路的频率很高,对于许多问题都要特别注意:

传输线必须加匹配。

对于同步时序电路,应该尽可能保证各条时钟线等长。

为保证时钟信号质量,时钟均采用差分传输。

不同的时钟线之间要保持一定的间距,以避免高速时钟信号之间的干扰。

合理设计匹配电阻的大小和位置。

SigNoise 是一个非常有用的仿真工具,它对于PCB 的仿真结果非常接近实际电路的情况,对于电子工程师的电路设计是非常有帮助的。同时,利用这个仿真工具,还可以灵活、方便的研究PCB 设计的一些问题。SigNoise 软件仿真结果形象直观、仿真功能齐全、模型库极易获得,是一个不可多得的好软件。