引言

嵌入式系统硬件的核心是各种类型的嵌入式处理器,目前全世界嵌入式处理器的品种已经超过1000多种,流行体系结构有30多个系列,嵌入式处理器一般可以分为嵌入式微处理器、嵌入式微控制器、嵌入式DSP处理器和嵌入式片上系统。

与标准微处理器相比,嵌入式微处理器只保留了和嵌入式应用有关的功能,并且为了满足嵌入式应用的特殊要求,在工作温度、抗电磁干扰、可靠性等方面都做了各种增强。

DSP嵌入式系统是DSP系统嵌入到应用电子系统中的一种通用系统,这种系统既具有DSP器件在数据处理方面的优势,又具有应用目标所需要的技术特征,在许多嵌入式应用领域,既需要在数据处理方面具有独特的优势的DSP,也需要在智能控制方面技高一筹的微处理器(MCU);因此,将DSP与MCU融合在一起的双核平台,将成为DSP技术发展的一种新潮流。德国Hyperstone公司是真正把DSP成功嵌入32位微处理器的厂商之一,尤其是它的E1-XS系列更是这方面的佼佼者。

1 E1-16XS微处理器结构概述

Hyperstone RISC/DSP架构框图如图1所示,Hyperstone内核是专为RISC和DSP功能的集成而设计的,但它不是两个不同内核在单个芯片上的简单组合,而是一个集成的内核和指令集。这一全集成的内核基于单处理器模式,带有单指令流。RISC和DSP单元间简单且高效的通信由1个96路的32位内部存储器实现,每个时钟周期内可以执行3条指令的操作,所以在100MHz的频率下可以达到300 MOPS这样优秀的性能。

Hyperstone E1-16XS是一款0.25μm CMOS工艺的微处理器,它结合了高性能的RISC微处理器和DSP处理器,利用简洁高效的指令,使嵌入式DSP处理器的实时性得以充分的发挥。 该处理器主要具有如下的特点:

1、32位RISC/DSP处理器ALU、DSP单元和Load/Store单元并行处理,内部集成硬件乘法器。

2、16根数据线,22根地址线,4个外部存储体(Memory Bank)选择信号。

3、4GB内存地址空间,I/O空间和存储空间分开寻址,存储器和DSP连接无需附加逻辑电路。

4、片内集成16KB RAM和片上指令高速缓存。

5、具有全面的DRAM和DMA控制器,所有的总线时序可编程。

6、片上PLL、CPU总高频率可达到180MHz。

7、中断服务程序可在7个时钟周期内启动。除内部中断外,还有7个外部中断可用。

8、3个可编程I/O引脚除了可配置成输入输出外,还可以配置成外部中断输入使用。

9、32位定时器和看门狗定时器,用户可利用hyRTK内核访问154个独立的"虚拟"定时器,仅需很少的处理开销。

2嵌入式系统硬件设计

2.1 系统硬件结构

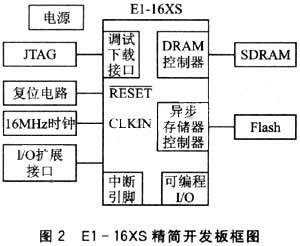

系统硬件结构如图2所示。

电源电路:输入5V,经过DC-DC变换,分别给微处理器提供2.5V和3.3V的电压。

晶振电路:16MHz有源晶体振荡器经过倍频,分别为Hyperstone内核/系统提供128/64MHz的时钟频率。

复位电路:可选用简单的RC复位电路,考虑到系统复位的可靠性和掉电监控,建议使用专门的复位IC,例如MAX706。

微处理器:即E1-16XS,是系统的工作和控制中心。

Flash:可存放Boot监控程序、嵌入式操作系统、用户应用程序或其他在系统掉电后需要保存的数据。

SDRAM:系统代码运行和数据变量存储的空间。

JTAG接口:通过该接口可对系统进行在线调试和程序下载。

I/O扩展接口:引出数据总线、地址总线和必需的I/O控制总线,便于用户根据自身的特定需求,扩展外围电路;DSP可以通过该扩展总线对其他板卡进行控制,或者其他板卡可以通过该接口对开发板进行操作。

2.2 系统主要硬件单元电路设计

不同的DSP处理器在与DRAM、Flash连接时通常会有些差异,所以下面着重分析存储器接口电路的工作原理和设计方法。

(1)Flash接口电路

由于Flash存储器具有低功耗、大容量,可整片或分扇区快速烧写、擦除、掉电后信息不丢失等特点,在各种嵌入式系统中得到广泛应用。

本系统中,Flash存储器采用Hynix的HY29LV160。他是16位数据宽度,存储容量为16Mb(2MB),可以在2.7-3.6V电压范围内进行读、编程(烧写)和擦除操作。

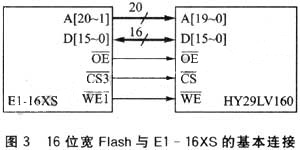

在大多数系统中,选用1片16位的Flash存储器芯片(单片容量有1MB、2MB、4MB、8MB等)构建16位的Flash存储系统已经足够。在此采用 1片HY29LV160构建16位的Flash存储器系统,图3为16位模式Flash与处理器E1-16XS的基本接法。

Flash存储器在系统中通常用于存放程序代码,系统上电或复位后从此获取指令并开始执行。因此,应将存有程序代码的Flash存储器配置到 Bank3,即将E1-16XS的CS3接至HY29LV160的片选端CE。输出使能端OE接E1-16XS的OE;写使能端WE接E1-16XS的 WE1,模式选择BYTE上拉,使HY29LV160工作在16位数据模式。RY/BY(就绪/忙)指示HY29LV160编程或擦除操作的工作状态。

HY29LV160地址总线A[19-0]与E1-16XS的地址总线A[20-1]相连;16位数据总线D[15-0]与E1-16XS的16位数据总线D[15-0相连,此时应将E1-16XS的BOOTB置为0,即选择外部Flash为16位工作方式。

(2)DRAM接口电路

与Flash存储器相比较,动态随机存储器DRAM虽然不具有掉电保持数据的特性,但其存取速度大大高于Flash存储器,在系统中主要用作程序的运行空间。

E1-16XS 内部的DRAM控制器支持DRAM的各种形式,例如Fast-Page Mode、EDO和SDRAM,都可以直接和处理器无缝连接。存储器存取的总线时序刷新控制等可由总线控制寄存器(BCR)设定,这里以目前嵌入式系统设计中常用的SDRAM说明电路的具体连接。

系统中SDRAM选用IS42S16100-7T。它的存储容量为 2Banks×512K×16位(2MB),工作电压为(3.3±0.3)V,16位数据宽度,如果用户需要运行嵌入式操作系统以及各种相对较复杂的功能,可以考虑增加SDRAM的容量,E1-16XS最大支持128MB。

图4为IS42S16100-7T SDRAM存储器和E1-16XS的连接框图,将该SDRAM配置到系统存储器的Bank0,即将E1-16XS的DP0(SDRAM选择信号)接至 IS42S16100的CS端,表1可以清晰地反应出E1-16XS和IS42S16100的连接情况。

(3)I/O扩展

由于DSP本身的I/O口相对比较少,在很多应用场合下,需要进行I/O扩展,E1-16XS内部I/O总线控制寄存器提供了6位作为芯片选择用,有就是可以连接64个周边器件;另外还有3位作为I/O器件内部寄存器地址寻址用,9位用来设定读写访问的总线时序设置,例如地址建立时间和保持时间等,这样可以降低对外设的访问速度,适应低速外设的要求,一般对外设I/O的访问连接如图5所示。

图5中,IORD和IOWR为I/O访问时的读控制信号和写控制信号,分别连接到I/O设计的读和写控制端;I/O设备的中断输出信号INT连接到DSP的中断输入信号INTn。E1-16XS提供了最多7个外部中断输入可供连接。

3 PCB板设计要点

设计好电路图后,就可以设计PCB板了,在系统中,E1-16XS的片内工作频率可以达到150MHz以上,系统总线频率也接近100MHz,因此,在PCB设计过程中,应该遵循高频电路设计的基本原则。首先应注意电源的质量与分配,其次要注意信号线和时钟线的分布。

(1)电源质量与分配

在设计PCB板时,给各个单元电路提供高质量的电源,会使系统的稳定性大幅度提高。一般应在电源进入印刷电路板的位置和靠近各器件的电源引脚处加上几十~几百μf的电容,以滤除电源噪声,还要注意在器件的电源和地之间加上0.01μF-0.1μF左右的电容,用来滤除元器件工作时产生的高频噪声,由于双面PCB板电源采用电源总线的方式,受到电路板面积的限制,一般存在较大的直流电阻,所以为了提高系统的稳定性,通常采用多层板,一般专门拿出两层,作为电源层和地层,而不在其上布信号线。低阻抗的电源层也可以像地层一样作为高频信号的返回通路,可以有效地降低噪声。

(2)同类型信号线的分布

在设计PCB时,对于处理器的输入输出信号中的数据线、地址线等相同类型的线应该成组、平行分布、并保持它们之间的长短差异不要太大,采用这种方式布线的既可以减少干扰,增加系统的稳定性,还可以简化布线,使PCB板的外观美观。

(3)时钟信号线的分布

较高频的时钟信号是电路板的关键信号,频率越高的时钟其布线要求也越高,布线时应使时钟源到负载的联线尽量短,线应尽量宽,不同时钟之间,时钟与其他信号之间避免平行走线。信号负载较多时,在一个驱动器上不要驱动其他时钟信号,保持时钟信号的质量良好。

结语

该精简开发板具有最小化的功能,用户仅仅需要在Flash里预先烧写Boot监控程序,就可以进行应用程序的调试和下载,该开发板具有良好的扩展性,通过I/O扩展接口为户的硬件扩展提供了很多的便利。用户可以在不更改Boot监控程序的前提下对该精简开发板进行硬件功能(串口、USB、可编程器件等)的扩充。