一种高CMRR和PSRR的共源共栅放大器.pdf

时间:08-22 13:16

查看:2261次

下载:163次

简介:

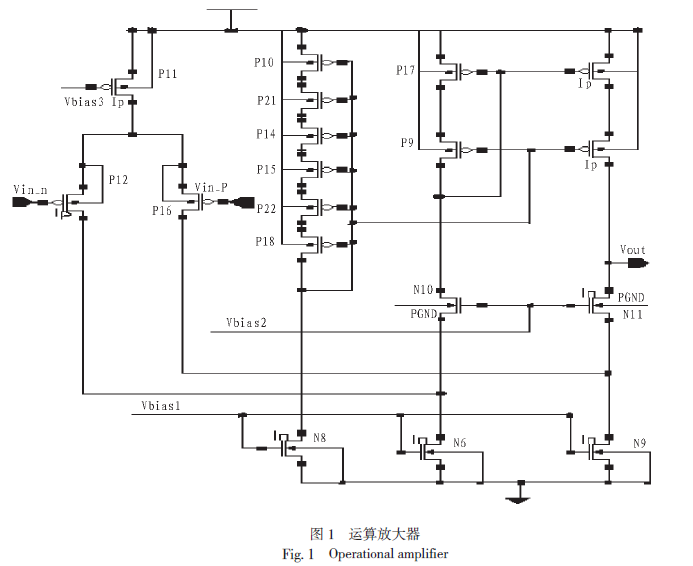

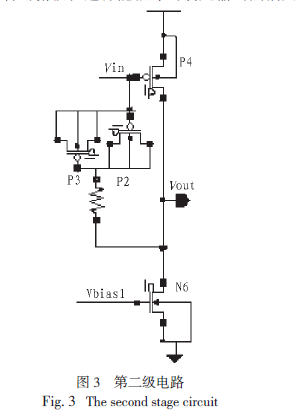

针对传统运算放大器共模抑制比和电源抑制比低的问题,设计了一种差分输入结构的折叠式共源共栅放大器。本设计采用两级结构,第一级为差分结构的折叠式共源共柵放大器,并采用MOS 管作为电阻,进一步提高增益、共模抑制比和电源电压抑制比;第二级采用以NMOS 为负载的共源放大器结构,提高增益和输出摆幅。基于LITE-ON40V 1.0 μm 工艺,采用Spectre 对电路进行仿真。仿真结果表明,电路交流增益为125.8 dB,相位裕度为62.8°,共模抑制比140.9 dB,电源电压抑制比125.5 dB。