基于FPGA的自适应锁相环设计.pdf

时间:01-15 10:57

查看:1390次

下载:162次

简介:

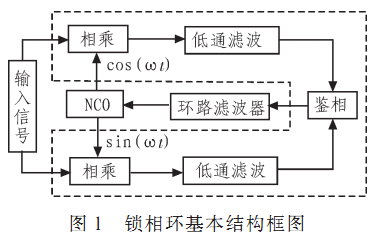

利用锁相环进行载波跟踪是获取本地载波的一种重要方法,针对锁相环的噪声性能和跟踪速度不能同时达到最优的限制,在锁相环PLL中引入自适应模块,根据环路所处的环境自适应对PLL环路参数做出调整。设计中利用仿真软件MATLAB对自适应锁相环进行仿真,并在FPGA硬件板上利用VHDL编程实现。在载波信号为10 MHz、采样率为80 MHz的条件下,设计的自适应锁相环在噪声水平较小时跟踪速度提高了0.5 μs左右,在噪声水平较高时相位抖动降低了0.01 rad左右。