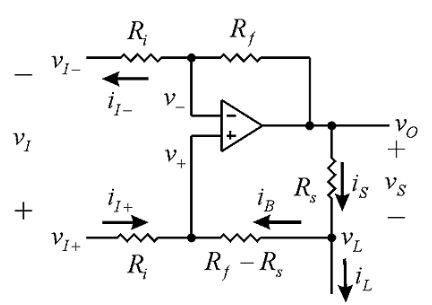

第一个要讨论的电路是运放电流镜,如下图所示。

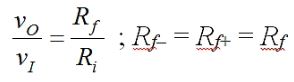

运放的反相(-)和同相(+)端输入电压等于:

当运放正常工作时,v-= v+,可以推导出:

运放输入电压仅取决于RL的参考地,它在相对于地的vL上浮动;

输出电流独立于vL和负载电阻RL。决定iL的是Rf+上的电压,这个电压必须与Rf-上的电压相同,而不管v-= v+是多少,而且Rf上的电压也不取决于地。

接着通过将输入源变为电压把电流镜修改为下图所示的第二种电路,并将Rf+返回到vR。

当v-= v+时,

首先,让vR = 0 V,形成单运放的差分放大器。在运放的输入电压相同(v-= v+),的情况下,

然后让vR=VOS,后者是恒定的偏置电压。得到

将Rf+连接到非地点的结果是将输出电压提高相同的数值。

对于vR的第三种变化,我们要耐心一些,并设vR= vO。针对要求的运放输入条件(v-=v+),vI=0V。vI≠ 0V的设置会使v+总是大于v-,运放输出将增加,直到达到其输出范围的上限。为了使电路正确工作(v-=v+),v+/vO必须小于1。在vO到Rf+处施加过大的电压将影响到vI乘vO,也就是:

这是施加到Rf+的反馈电压必须降低的数值。

为了使正反馈路径实现这个压降,可以将Rf+分解成两个串联电阻Rf-Rs和 Rs。除了Rf-Rs中的 iB电流外,使得Rs上流经额外的电流(iL)便能实现额外的压降。

为了通过分离iL和iB简化电流,中间电路有一个 a ×1电压放大器插入到缓冲器iB中,使得Rs中只流过iL。电路如下所示。

在已知Rs及其电压vs和电流is的情况下,

运放的输入电压等于:

和前面一样,其中的iI=iI-=iI+。然后替代vL,得到以下的输入电压公式:

最终的输出电流:

iL独立于vL;上面的iL公式中没有出现vL,公式只与vI有关。如果RL增加造成vL增加,那么放大是围绕正反馈环路实现的。vL中的vl增量变化被放大,并以下面的增量幅度改变vO:

H+是从vO到v+的正路径反馈除数。然后v+被放大同相运放增益Av+倍。结果是,从vl到vO的增益等于1;vO随vl变化,并自举提升vL电压,因此vS不发生改变。这样,iS保持不变,vL由于这个自举行为不影响iL。

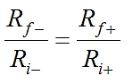

最后,在没有×1缓冲器的情况下,我们可以有下图所示的Howland电流源。Rf+被分解为两个串联电阻Rf-Rs和Rs,因此总电阻保持与前面相同,以满足电流源条件。

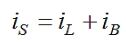

在缓冲源上面增加的复杂性表现为如今iL和iB是不分开的,而是一起流经Rs,其值为:

不过这两个电流还是可以通过应用一些源平移定理等电路操作分开来。将Rs分解成iL和 iB,两个电路,如下图所示。左图是反馈电路的一部分,右图是输出电路的一部分。

反馈路径的总串联电阻仍然是Rf,vL则从vO减少了vS,跟前面一样,加上在Rf的Rs部分下降的电压iB。电流源条件保持不变:

也就是说,正反馈路径和负反馈路径的Rf/Ri比值必须相等。然后电压自举行为保持iL独立于vL。