1 引言

随着数字信号处理器性能的不断提高及其成本与售价的大幅下降,数字信号处理应用领域飞速扩展,信号处理进入了一个新的发展时期。同时随着计算机技术以及互联网络技术的不断发展,越来越多的数据需要经过计算机来进行处理、存储、传输筹操作。计算机的应用已经遍及我们生活的每一个角落。由于计算机本身的特点,通用计算机通常仅负责没有实时性要求的工作,而不适于进行实时性要求很高的数字信号处理。将计算机和DSP有机地结合起来,充分利用各自的优点,它们将会相得益彰,满足现实应用中对数据实时处理能力、数据传输能力以及数据管理能力提出的越来越高的要求。PCI总线以其众多优点在计算机中具有不可取代的作用,采用PCI总线使DSP与计算机通信可以很好地满足其对高速数据传输的要求。本文以实际开发系统为背景,以TI公司的TMS320VC5402与PLX公司的PCI9052为基础。详细论述了基于DSP的PCI总线结构的数据采集系统硬件及软件设计方案和实现方法。

2 数据采集系统硬件设计

2.1 系统结构及原理

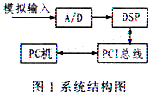

基于DSP的PCI总线高速数据采集系统的结构如图1所示,它主要由A/D转换器、DSP数据读取及处理、PCI通信接口和PC机等部分组成。模拟信号经A/D采样后由DSP通过并行I/O读取,并将处理后的数据通过PCI总线送到通用计算机做进一步处理[1]。

A/D转换器采用TI公司的TLC5510,TLC5510为8 bit、20 MS/s的高速并行A/D转换器。TLC5510在每个时钟的下降沿采样,该采样点的转换数据经过2.5个延迟后,在时钟的上升沿输出,也就是每个点的转换时间为2.5个时钟周期,一旦转换流水线启动,则在每个时钟的上升沿都有一个转换数据输出。

DSP与计算机之间的通信由接口电路 PCI9052实现。PCI9052是PLX公司推出的一种简单、高效的PCI从设备接口,可实现多种外设局部总线和PCI总线的互连。根据PCI规范,主设备和从设备的划分本质上是确定数据传输双方访问与被访问的能力和关系。在此,PCI9052只能由主机或其它拥有总线主控制能力的设备进行数据的读写操作。但由于其内部有64Byte写FIFO和32Byte读FIFO,使PCI9052的局部总线和PCI总线能互相独立工作,可支持传输速度为132 Mb/s的突发传输[2]。

DSP采用TI公司的TMS320VC5402,它的处理能力可达到100 Mb/s,具有改进型的8位HPI接口,有16 K*16 Bit DARAM,以及4 K*l6 Bit ROM存储空间。具有较高的性价比[3]。

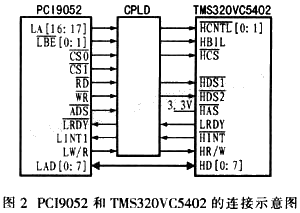

2.2 PCI9052与TMS320VC5402的接口

PCI9052的局部总线设置为8位局部总线,采用地址数据非复用模式,PCI9052和TMS320VC5402的接口电路如图2所示 [4,5]。此时,LBE1为LA1,LBE0为LA0。将PCI9052的LBE0接HPI的HBIL,用以区分第一字节和第二字节。PCI9052的 LA17接TMS320VC5402的HCNTL1,LA16接HC-NTL0,以选择HPI寄存器。PCI9052的LAD[0:7]接 TMS320VC5402的HD[7:0]。TMS320VC5402的HINT反向后接至PCI9052的LINT1,之所以反向是由于HINT低电平有效,而UNT1是高电平有效。PCI9052的LW/R反向后接至TMS320VC5402的HR/W,因为LW/R高电平表示写,低电平表示读;而 HR/W高电平表示主机要读HPI,低电平表示主机要写HPI。PCI9052的CS0与CS1相或后连接至HCS,RD和WR分别连接到 HDS1,HDS2。TMS320VC5402的LRDY通过一定的逻辑组合再加上一个D触发器与PCI9052的LRDY相连以实现PCI9052与 HPI的同步。PCI9052局部时钟采用40MHz。其中CPLD选用EPM7128,使用MAX+PLUSⅡ进行设计。

HPI主机接口采用访问寄存器的方式来进行DSP内部数据的读写,把HPI口单纯映射到PCI的I/O空间或者存储器空间都有不可避免的缺点,因此本接口电路采用双映射方式,利用映射来访问控制、地址寄存器和单个数据口,而利用存储器映射来访问连续数据口。以实现TMS320VC5402与 PCI9052之间方便、高效的数据通信[6]。

3 数据采集系统软件的设计

数据采集系统的软件设计包括三个部分:DSP上的采集程序及响应程序。数据采集卡的驱动程序,在驱动程序上构建的应用程序。驱动程序是实现DSP与计算机通信的关键,本文主要介绍设备驱动模型及其初始化的设计方法。

3.1 驱动程序模型

Win2000不支持直接访问硬件,虚拟驱动器依赖运行在内核模式的真正的驱动器。内核模式驱动程序使用系统级代码编写,且运行在内核模式下,因为内核模式允许直接硬件访问。内核驱动程序可被进一步分成遗留模式的驱动程序和Windows驱动模式的驱动程序(WDM)。

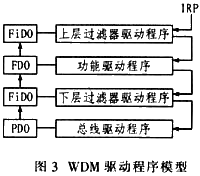

Windows 驱动程序模型(WDM)如图3所示。图中左边是一个设备对象堆栈。设备对象是系统为帮助软件管理硬件而创建的数据结构。处于堆栈最底层的设备对象称为物理设备对象(PDO)。在设备对象堆栈的中间某处有一个功能设备对象(FDO)。FDO的上面和下面还会有一些过滤设备对象。位于FDO上面的过滤设备对象称为上层过滤器,位于FDO下面的过滤器设备对象称为下层过滤器。

总线驱动器的任务之一就是枚举总线上的设备。并为每个设备创建一个PDO。一旦总线驱动器程序检查到新硬件存在,PnP管理器就创建一个PDO,创建完PDO后,PnP管理器参照注册表中的信息查找与这个PDO相关的过滤器和功能驱动程序。系统安装程序负责这些注册表项,而驱动程序包中控制硬件安装的INF文件负责添加其他表项。这些表项定义了过滤器和功能驱动程序在堆栈中的次序。

3.2 驱动程序的初始化

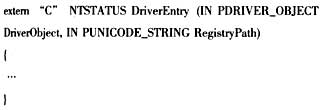

PnP管理器先装入硬件需要的驱动程序,然后再调用驱动程序中的 AddDevice函数。一个驱动程序可以被多个类似的硬件使用。但驱动程序的某些全局初始化操作只能在第一次被装入时执行一次。而 DriverEntry例程就是用于这个目的。DriverEntry是内核模式驱动程序主入口点常用的名字。I/O管理器按下面方式调用该例程:

DriverEntry的第一个参数是一个指针,指向一个被初始化的驱动程序对象,该对象代表用户的驱动程序。DriverEntry的第二个参数是设备服务键键名,其主要工作是把各种函数指针填入驱动程序对象。这些指针为操作系统指明了驱动程序容器中各种子例程的位置。

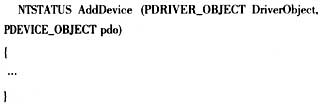

PnP 管理器先装入最底层的过滤器驱动程序并调用其AddDevice函数。该函数创建一个FiDO,这样就在过滤器驱动程序和FiDO之间建立了水平连接。然后AddDevice把PDO连接到FiDO上。PnP管理器继续下上执行,装入并调用每个底层过滤器、功能驱动程序、高层过滤器,直到完成这个堆栈。该函数的原型如下:

DriverObject参数指向一个驱动程序对象,就是在DriverEntry例程中初始化的那个驱动程序对象。PDO参数指向设备堆栈底部的物理设备对象。AddDevice函数的基本任务是创建一个设备对象并把它连接到以PDO为底的设备堆栈中。

当 AddDevice函数将FDO和FiDO创建且连接好后,PnP管理器分配资源且发送PRP_MN_START_DEVICE,功能驱动程序需要在这个 IRP上做大量工作,包括分配并配置额外的软件资源以及为设备操作做准备。处理这个IRP主要通过PnPStartDevice函数完成。 PnPStartDevice函数首先将IRP传递到底层驱动程序。等待完成后,调用IoGetCurrentIrpStackLocation函数得到当前自己的堆栈单元。I/O堆栈单元的Parameters联合有一个名为StarDevice的子结构,该结构包含了资源分配信息。在 StarDevice里就可以将分配的资源填充到PDO的设备扩展域中,并且调用IoConnectInterrupt函数连接中断。

层次结构可以使I/O请求过程更加明了。每个影响到设备的操作都使用I/O请求包。通常IRP先被送到设备堆栈的最上层驱动程序,然后逐渐过滤到下面的驱动程序。内核通常通过发送I/O请求包(IRP)来运行驱动程序中的代码。

4 结束语

基于DSP的PCI总线数据采集系统充分利用了DSP丰富的内部资源、强大的数字信号处理能力及PCI总线的高传输速度,能够方便的开发数据压缩、语音压缩存储等新功能信号,并进行预处理与分析处理。通过PCI总线进行数据传送可大大提高传输速度。本系统适用于高速数据的采集和处理以及需要进行大量数据传输的应用场合。